Other Parts Discussed in Thread: TIDA-010247

Hello,

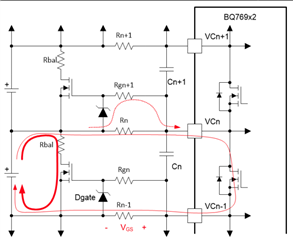

We are using stacked bq76952 configuration as per TIDA-010247 reference design. Up until now we've been balancing alternate cells, recently we decided to use the adjacent cell balancing feature.

When 2-3 adjacent cells are being balanced it works fine, but when the number of balancing cells increases further the AFE starts to overheat and reach around 90-100 degree Celsius (Observed via thermal camera), and the internal temperature cutoff of the AFE turns off the balancing.

We are using Rbal = 22 Ohm, Rn and Rn-1 = 100 Ohms, Rgn = 10 kOhm and Cn as 220 nF

The Gate Threshold voltage of the external NFET is ~0.8V

And the input cell voltage was around ~ 4V

What would be your recommended solution for this

Thank you