Hi TI Team,

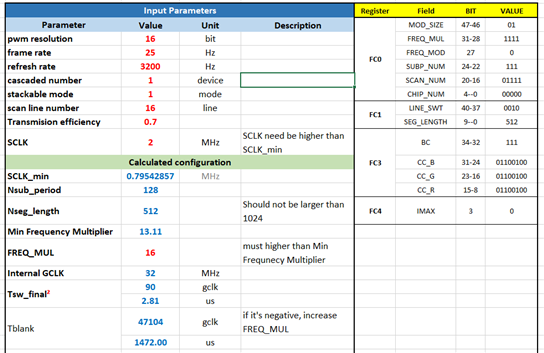

After much experimentation with an STM32G071 Nucleo board, I have still not been able to achieve lighting up the LP5890 EVM board. I have gone through the supplied sample code and converted it to STM32 HAL drivers. I have also used the LP5890 Register Map Generation Tool to make sure the registers are setup correctly.

I am currently running my SPI at 2MHz Baud Rate. I have set up a timer to run continuously at this same frequency.

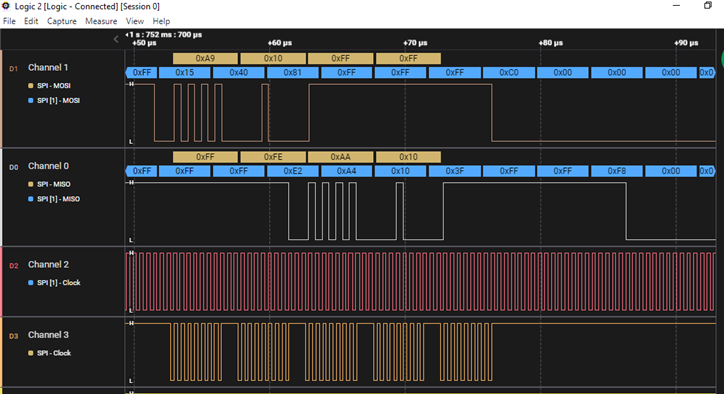

Here is a screenshot of what I'm currently seeing:

Channel 2 is the timer setup to be the clock, it is attached to SCLK on the EVM board. Channel 3 is the actual SPI clock on the Nucleo board. I am getting the same thing back (0xAA10 for W_CHIP_INDEX) on the MISO line that I am putting out on the MOSI. I am not seeing any other movement on the SPI lines besides this.