Other Parts Discussed in Thread: TPS2660, SN74LVC1G14

Hi Team,

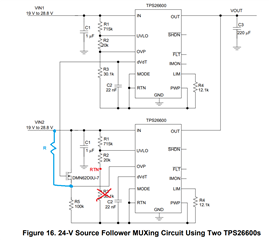

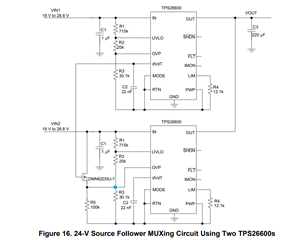

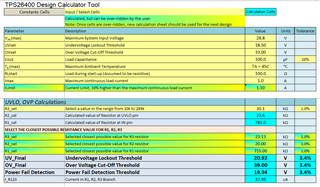

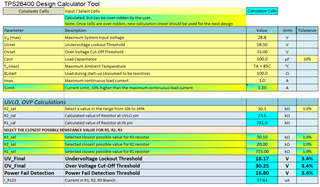

Can you suggest most simple power mux with TPS2640 ( there is no need for fast switchover time). ( eg FLT and SHDN pin)

Input 1 ( Always has priority)

Vin1 from 12V to 24V

Input 2

Vin2 from 5V to 25V - but it should only work from 12V to 24V ( when 5V then it is UV lockout activated)

-> when only input1 connected it powers output from 12V to 24V

-> when only input2 connected it powers output from 12V to 24V ( 5V to 12V is in UVLO)

-> when input1 and input2 connected, if input1 (from 12V to 24V) then input1 powers output regardless of input2 voltage

-> when input1 and input2 connected, if input1 (in UVLO or OVP state) then input2 powers output .

In this case when input 2 powers output and input1 in UVLO, will the current flow from input2 to input1 through reverse current blocking mosfet of the efuse1 ?

Best Regards,

d.