Hi Sir,

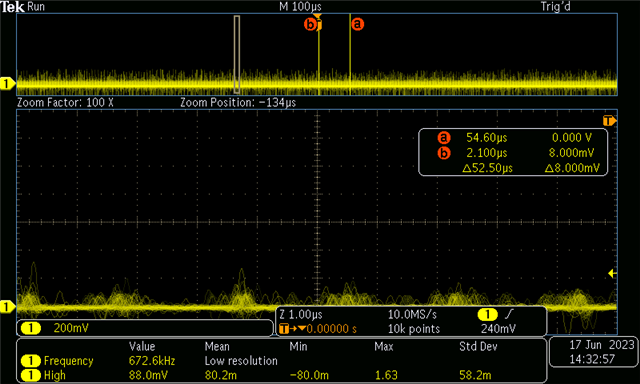

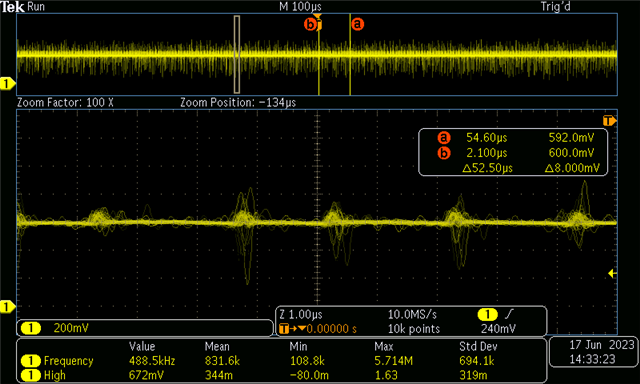

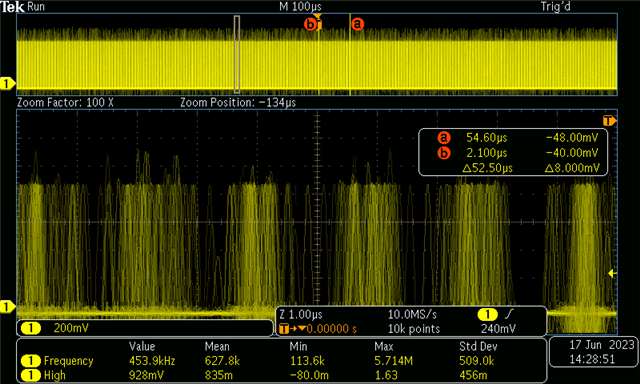

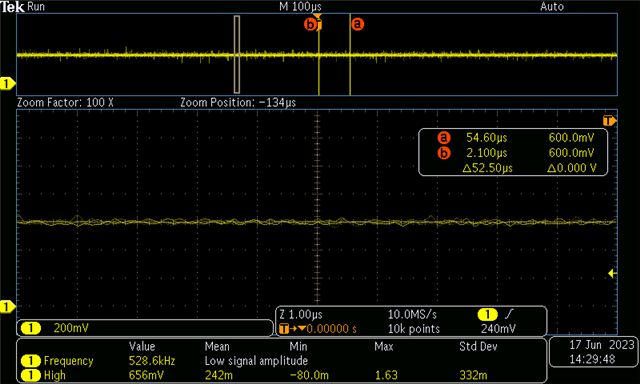

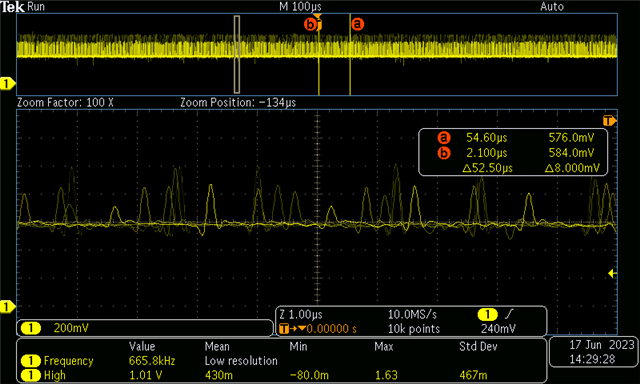

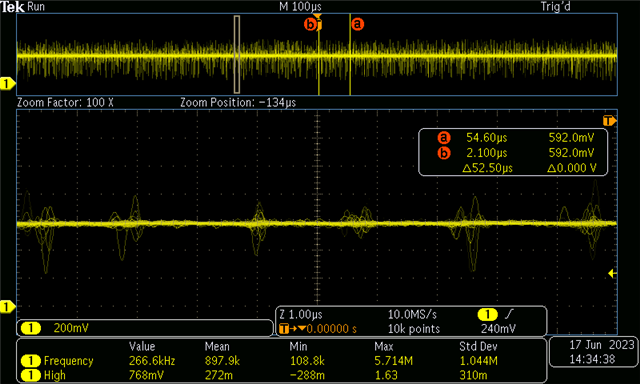

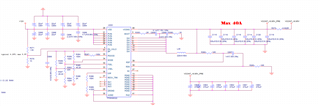

My customer use TPS548D22 for 0.85Voutput , 40A application with FPGA. Please check the attached circuit and waveform in light load.

https://drive.google.com/drive/folders/1I2gkKqkCKEj3i4JOz7W94IiMy7uBwnoj

1. Is the waveform looks ok? Any design issue on their circuit?

2. When the load is on, Vout will down to 0.6V and FPGA will not work correctly. Any comment or testing for customer?

Thanks for your kindly help.

Best regards,

Gary Teng