Other Parts Discussed in Thread: TPS2663, CSD19502Q5B, TPS2490

Hello.

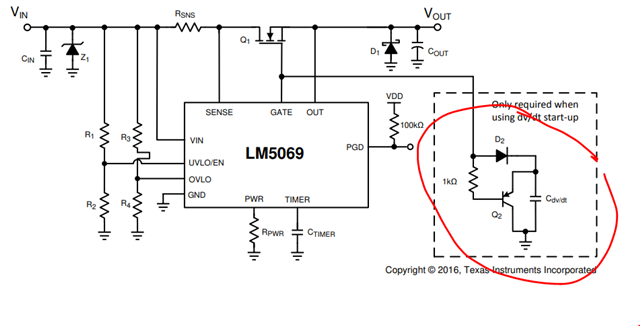

We are planning to use LM5069 in a configuration as below:

- Input voltage nominal = 50V

- Max load current (Pulsed current, 1ms pulse width with 20% duty cycle) = 12A

- Output capacitance = 1000uF

- Max ambient operating temp = 75C

- Need reverse polarity (not through schottky Diode but through MOSFET itself to minimize the IR drop)

- UV/OV protection at 48V/52V

dv/dt start up needed to manage power limit at start-up

TVS protection at input of the device.

We have checked the LM5069 design calculator. But we are not able to ascertain the correct MOSFET selection with this pulsed current, to meet the junction temp and SOA. Once the MOSFET is fully ON, the pulsed load current shall be applied as listed above.

Can you please help on this?