Hello,

My customer is using the TPS40345 as FPGA core power supply.

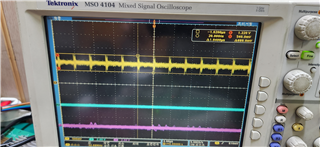

Below is the output ripple capture image. The measured output ripple characteristic is significantly worse than guided by the datasheet.

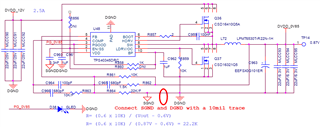

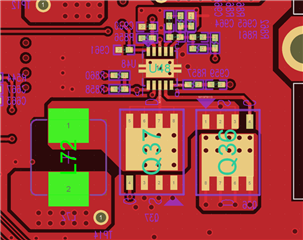

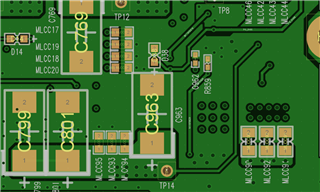

Below are the customer design files and inductor datasheet.

LPMT6530-1H Series DataSheet_210219 (1).pdf

Q1 ) Please review whether there is a problem with the design of the TPS40345.

Q2 ) Please advise on how to improve the output ripple characteristics.

Thank you.

JH