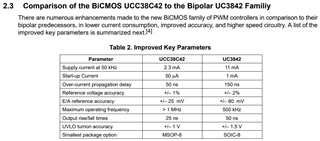

Other Parts Discussed in Thread: UC3845, UC3843, UC3842, , UC3843A

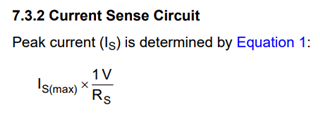

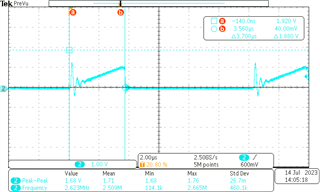

Non-isolated HV DC/DC (24VDC to 600VDC) with voltage closed loop control does not hold load. Output voltage starts dropping with increased load even though DC is about 43% (much lower than limit and primary current does not show any signs of saturation. Any suggestions? Thanks.