Hi, team:

Nice to meet you!

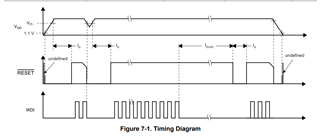

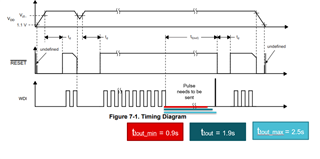

Could you help explain the principle of watchdog, and could you help confirm the minimum time of watchdog time? should it be smaller than 0.9s?

Why the time range like 0.9-2.5s? due to in my customer product, the flash erase time is 1s, could you help check the reset risk during the erasing process?

Hope to get your reply, thanks.