Other Parts Discussed in Thread: LM76002,

Hi team,

My customer is asking about the tss (soft start time.)

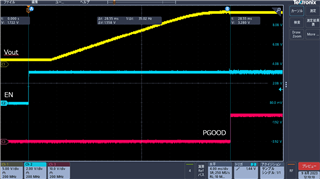

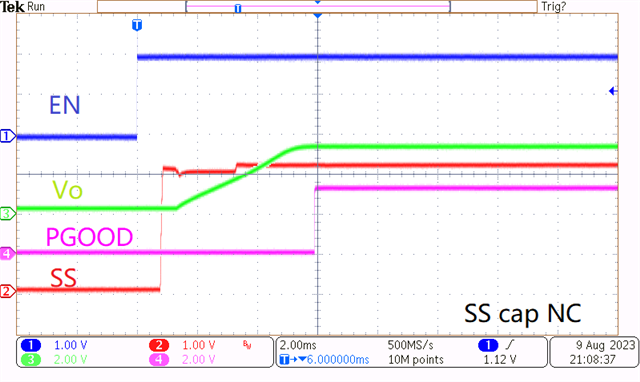

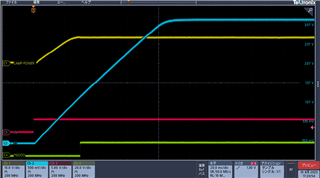

The definition is "CSS = OPEN, from EN rising edge to PGOOD rising edge"

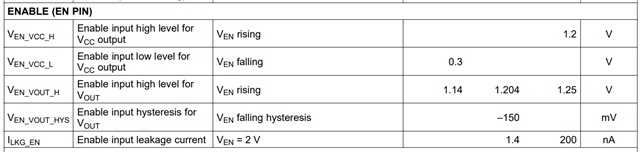

In the datasheet, EN rising is defined as:

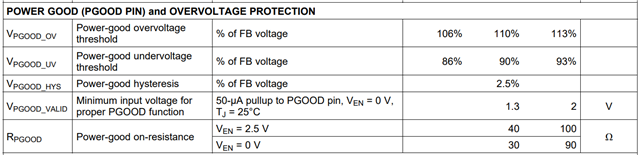

, and PGOOD rising is defined as:

.

.

The power good does not talk about the timing.

With that said, how would you define the soft start time?

My understanding is the time between "the EN reaches 1.2V" and "PGOOD reaches 50% of the defined voltage (Vcc/2)".

Please let me know.

Thanks,

Luke