Other Parts Discussed in Thread: TPS3823, TPS3828, , TPS3824

Hi team,

My customer wants to disable the WDT and set /RESET to high when read/write event at MCU.

In the datasheet, it says that /RESET will be LOW for td when there is no input in the WDI for Ttout. But my customer wants to disable this feature only at particular event.

I guess this can be achieved by below feature:

"The watchdog timer can be disabled by disconnecting the WDI pin from the system. If the WDI pin detects that it is in a high-impedance state, the TPS3820, TPS3823, TPS3824, or TPS3828 will generate its own WDI pulse to ensure that RESET does not assert."

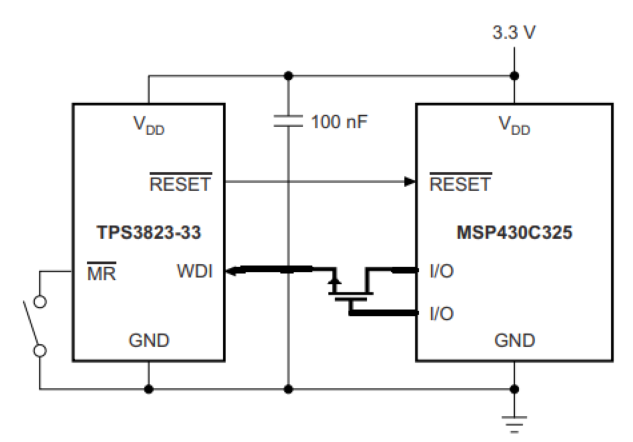

Could you show us the recommended schematic/configuration for disabling the WDT. Shoud the customer use FET at the WDI and control it by the GPIO from MCU?

Regards,

Ohashi