Other Parts Discussed in Thread: UCC28070,

Hello,

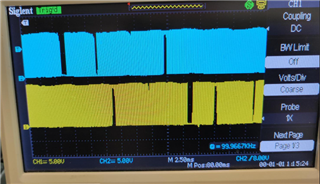

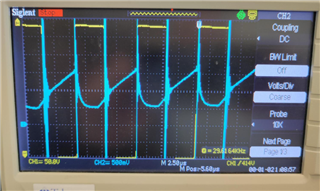

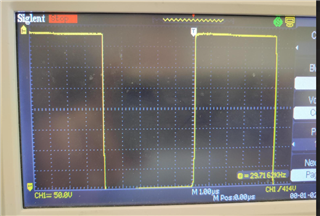

The problem I am facing is that driver outputs of UCC28070 are simultaneously switching during both half-waves.

Usually first half wave only Q1 should switching and second half wave Q2 takes place.

The power factor is ok, but that strange behavior makes the efficiency to drop significantly after certain power ( after 50% load )

I have attached schematics and wave diagrams.