Hi TI expert,

I have issue when using LM5066I as power monitor and management in project.

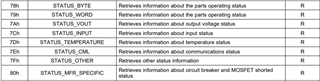

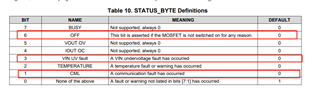

The SMBA pin output low randomly after board is powered up, and I tried to read the STATUS_BYTE register(0X78h) which has default value 01h, but it was 4Bh. According to the datasheet, then it indicates there are multiple fault happened.

Except the bit 6(it could be set by chip automatically if there is any warning or fault), there are another 2 faults which are VIN undervoltage(bit3) and communication fault(bit1).

We captured the VIN by scope when the SMBA pulls low, but the VIN seems quite stable, so it should not be a real VIN undervoltage; and the communication fault, I've no idea why it happens, even after the SMBA pulls low , I could read the chip by i2c normally which means the communication works.

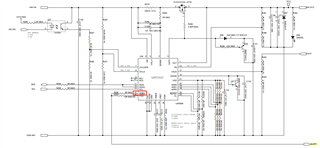

Can you help analyze it and a relevant capture of schematic as shown below:

Thanks,

JKW