Hello,

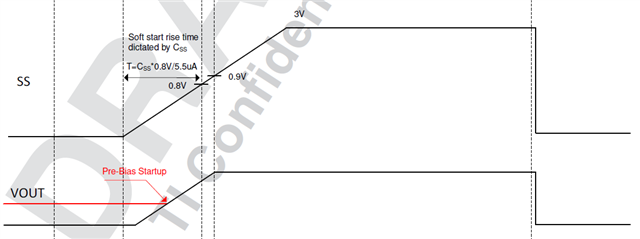

Looking at the data sheet for TPS65261-1, it states that PGOOD rising edge deglitch time is 512 cycles.

This value is TYP, do you have MIN and MAX information?

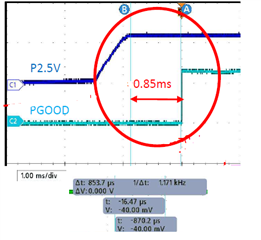

In my circuit, the switching frequency is 781kHz, but when I actually measure my circuit, the PGOOD deglitch time is 0.85ms.

In the calculation above with 512 cycles, it should be 0.655ms.

This difference appears to be large even when variations in switching frequency are considered.

Best regards,