Hi there,

I'm currently designing with TPS922055 and am using this part to drive 5x LEDs in series. The Vf for each LED is something like 3.5V each worst case. I am setting the max current through this LED chain to 1A. My Vin for this circuit is 20V. The circuit looks very similar to the application example given in figure 9.2.1. in the data sheet

At 3.5V x 5 LEDs I have an aggregate Vf of 17.5V. This leaves 2.5V of headroom between my 20V input. If I assume I can be as low as 19V on my input, I'm left with 1.5V of headroom between Vf and my rail. Additionally, 1.5V is very close to the 1.2V comparator voltage against which UVP is measured, and even if I DNI R2 and 0ohm R1 (referring here to the voltage divider on UVP shown in figure 9.2.1) I'm not left with much room vs the 1.2V comparator threshold of UVP and run the risk of a false fault.

To get around this, I'm considering tying UVP directly to Vout (which is more-or-less just Vin rail at the beginning of the LED chain), so that we never run the risk of tripping UVP. I understand I lose protection against an LED- short to PGND, but that may not matter so much for my application.

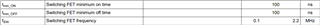

The question is, what is my LED driver headroom should I forego the UVP feature by tying the UVP pin to Vout? Is it just the Rdson of the internal FET (0.15ohms) multiplied by my current being sourced to the LED string (max 1A, in my application) for a total of 0.15V? What implication does coming so close to this headroom limit have on the efficiency of the TPS922055?

Are there any other pitfalls to consider here while running this circuit with a high-ish aggregate Vf vs its input voltage?

Thanks!

Rob