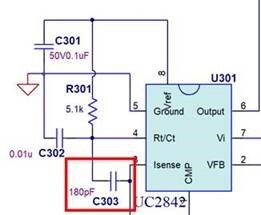

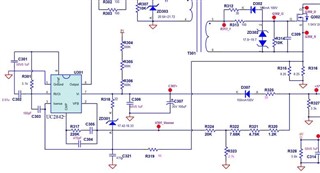

Other Parts Discussed in Thread: UC2844A

Customer fund that the duty cycle would be unstable at quite light load and certain input condition. However, when C303 is added between Pin3 and Pin4, the problem is gone. We'd like to know the knowledge behind why this cap is able to solve the problem and is this related to the slop compensation? Is there application note talking about this cap in Flyback application?

Regards

Brian