Hi All,

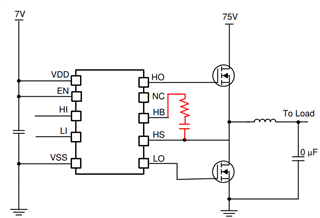

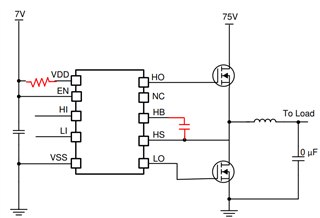

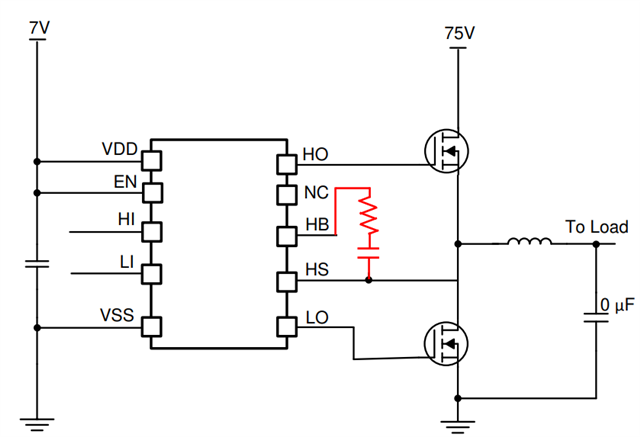

I have a question regarding UCC27282.

How much current can be continuously passed through the built-in bootstrap diode?

Also, what is the maximum value of pulse current? For example, I would like to check how much current can flow when initially charging the bootstrap capacitor.

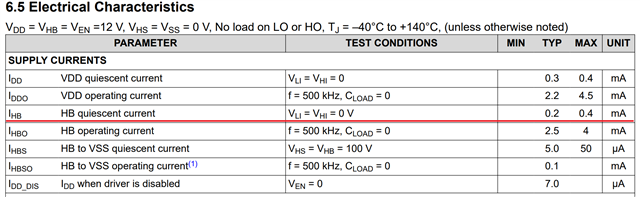

The maximum value of HB quiescent current (IHB) in 6.5 Electrical Characteristics is 0.4mA.

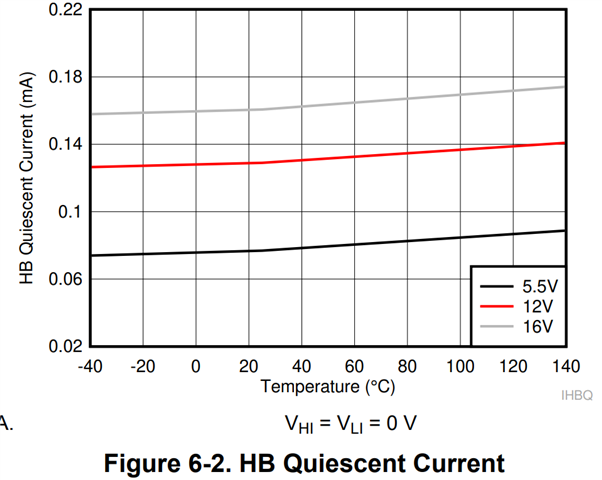

Figure 6-2. HB Quiescent Current is 0.18mA at maximum.

What's the difference? Is the maximum 0.4mA due to device variations? Or are there other conditions?

Best Regards,

Ishiwata