Other Parts Discussed in Thread: TPS546A24A

Hi Team,

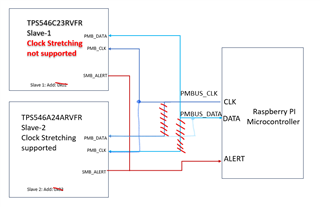

I have done a design using TPS546C23RVFR and TPS546A24ARVFR.Both device PMBus lanes are connected to a single mater via common PMbus.Looks TPS546A24ARVFR device supports PMBUs clock stretching feature ,but TPS546C23RVFR device doesn't support clock stretching feature.Will this PMBus communcation work with 2 slaves and master?.i have attached below mater slave connection.

Please check and let me know what can be

/cfs-file/__key/communityserver-discussions-components-files/196/pastedimage1708452075243v2.png

Datasheet TPS546C23RVFR : /cfs-file/__key/communityserver-discussions-components-files/196/pastedimage1708452165879v3.png

Does this both device support clock stretching TPS546C23RVFR and TPS546A24ARVFR ?

Regards,

Sujith M