Hello expert,

Are there some possibility to cause ACT wave from 1 to 0?

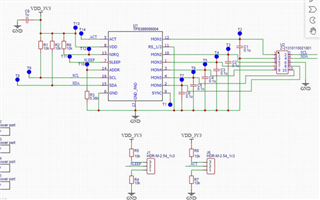

Situation 1: ACT is pull up to VVDD_3V3 through R8, As shown in the following picture, ACT is driven to 0 about 1.5ms and than turn back to 1.

Situation 2: ACT is pull up to VDD_3V3 directly. The ACT will not be drive to low but there is a high noise spike.

Best regards,

wenting