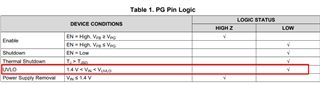

We're employing the TLV62568AP buck regulator for the conversion of 5V to 1.8V. To achieve a logic LOW voltage at the PG pin of the regulator, our focus is on the condition highlighted in red.

Do we require additional device conditions, such as the status of the EN pin, to achieve a LOW PG (power good) signal under the input voltage condition of 1.4 V < VIN < VUVLO?.