Other Parts Discussed in Thread: AM6412, TPS22965, TPS6521905

Hi All,

I have to study the most compact possible solution powering a SITARA AM6412 and I found some PMIC references that may be could suit the situation.

( the only interfaces w'ill use are QSPI,PCIE,UART)

Here are some questions about TPS6522053 and 65219 variants(from 01 to 08, plus 0C).

1 - Because there are a lot of variants, is there a document explaining the differences between this parts ?(the SLVAFE9 stops at 6521904) ?

2 - Can you explain the purpose of the FSD feature that is enabled by default on TPS6522053, and TPS6521901 to 04.

- does "first" mean : first time the part ever sees the power, or does it mean every time it sees the power therefore bypassing the EN input signal control (we DO want an enable control) ?

- Perhaps FSD only applies to the I2C function which has to be operational continuously and not the DC/DC and LDO functions. Please explain.

3 - Among all the variants is there one that can be programmed "at home" ?

4 - how can we disable FSD for parts where this feature is by default enabled and which are not programmable at home ?

5 - What would be wrong when using the 3V3 LDO1 output to source the AM6412 3V3 pins such as VDDSHV_MCU and others (considering total current < 400 mA) ? All the examples use an additional TPS22965

6 - Can you explain the concept of "Bypass" versus "load switch" relative to LDO1? . Isn'it the same when LDO-VIN=3,3V and we want LDO-Vout=3,3V ?

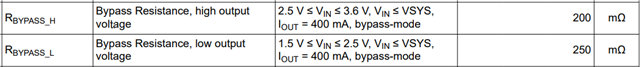

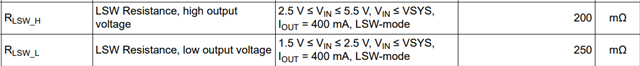

7- Supposing LDO-VIN = 3.3 and LDO1 configured in bypass mode(default) should we expect LDO1-VOUT be equal (worst case) to 3.3-0.2*0.4 (due to Bypass resistance) = 3.22V ? or should we consider we loss at least 300mV dropout ?

8 - Same question when LDO1 configured in load switch mode : only 0.2 Ohm Rswitch has to be taken into account ?

9 - in the SKAM64 EVM we can notice that LDO1_VIN=3.3V expecting LDO1_VOUT=3.3V despite the "by_default" bypass mode of the TPS6522053. How is this managed ?

With best regards,

Bruno