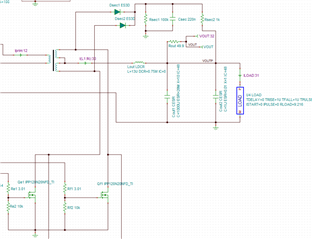

Other Parts Discussed in Thread: UCC28950

Hello,

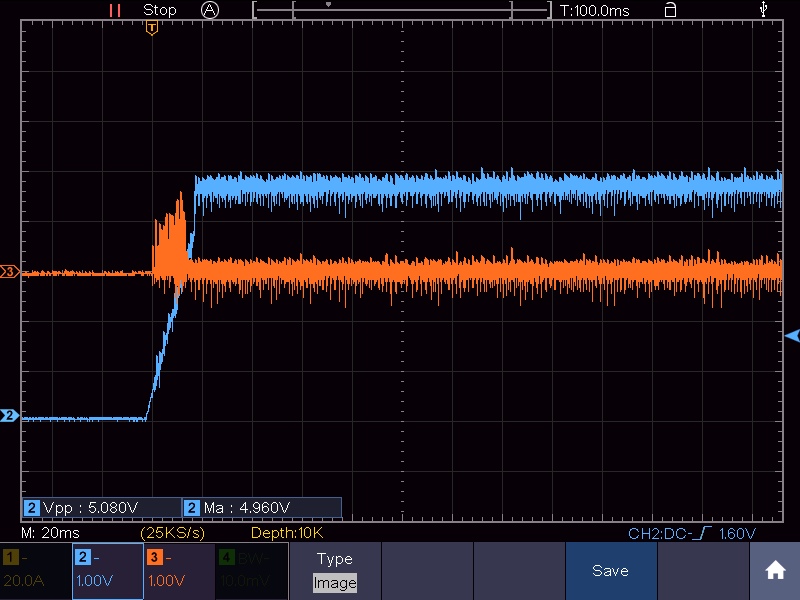

While testing a 2.5kW PSFB design, it is successfully working and giving expected 48V output at 10% load (5.3 A). But as the load is increased to around 8-9A, MOSFETs B and C are getting damaged (all legs shorted). Thus, shorting the input.

Visible burn marks can be seen on the thermal tape of the heat sinks of AB leg. (Indicating B is getting more heated compared to C which was also shorted but had no burn marks on the thermal tape of heatsink).

MOSFETs A and D were fine.

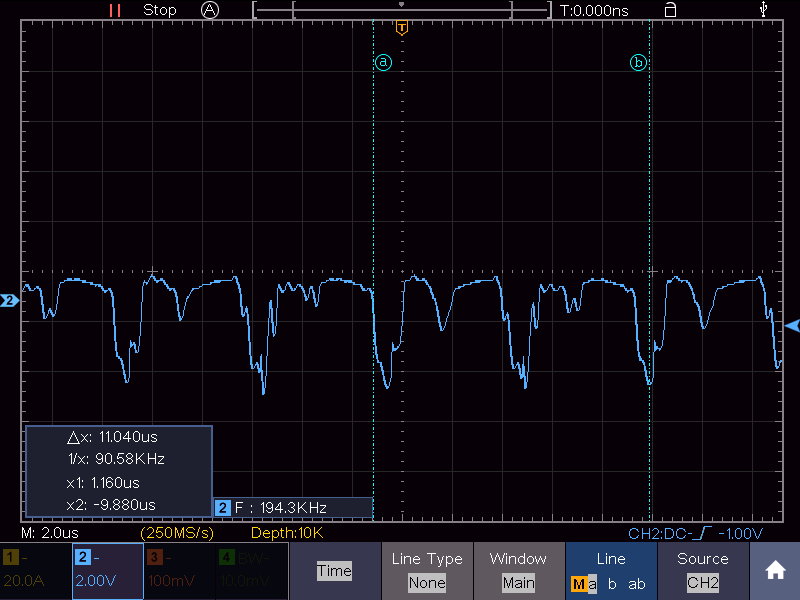

As expected MOSFETs A and B are not operating at ZVS at 10% load, unlike CD leg which is operating at ZVS and is comparatively less heated.

Blue: Vds of MOSFET B;

Orange: Vgs of MOSFET B

The Primary side MOSFETs used are (IPP65R110CFDXKSA2) and the heatsink used is (SK 481 50 - Fischer Elektronik).

How can the MOSFETs B and C be prevented from getting damaged?

Regards,

Nishant S