Hi,

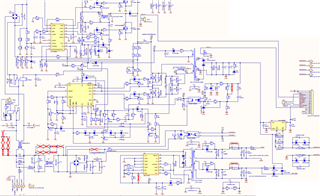

In continuation of the previous post which I made ("UCC28061: Power MOSFETs blown up sometimes") I want to share the new measurement with you and exploring the possible issue with the MOSFETs in this design.

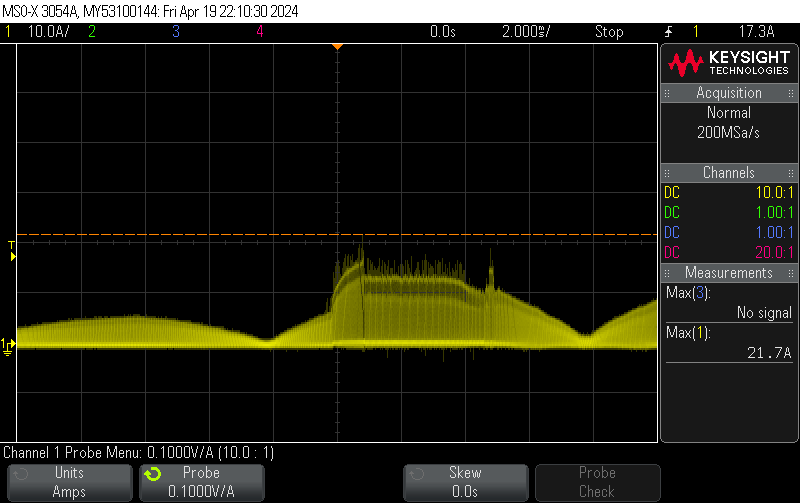

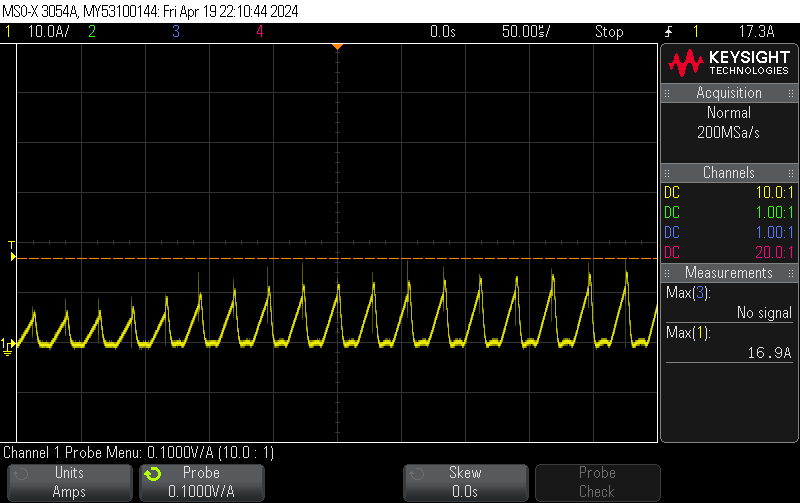

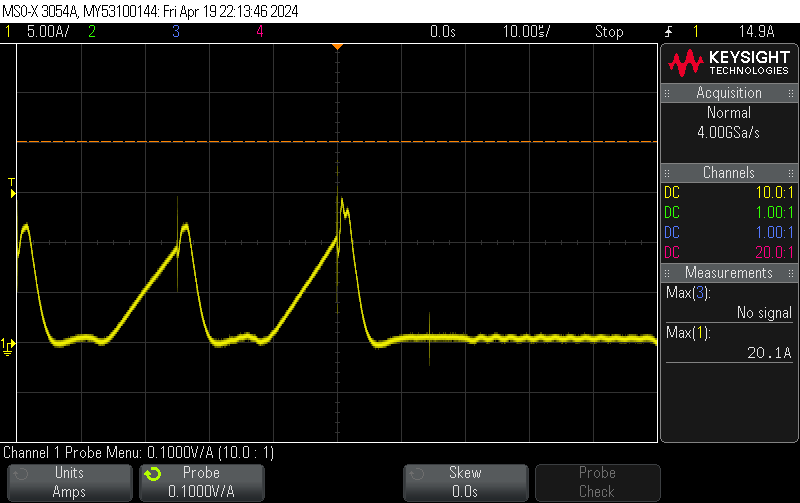

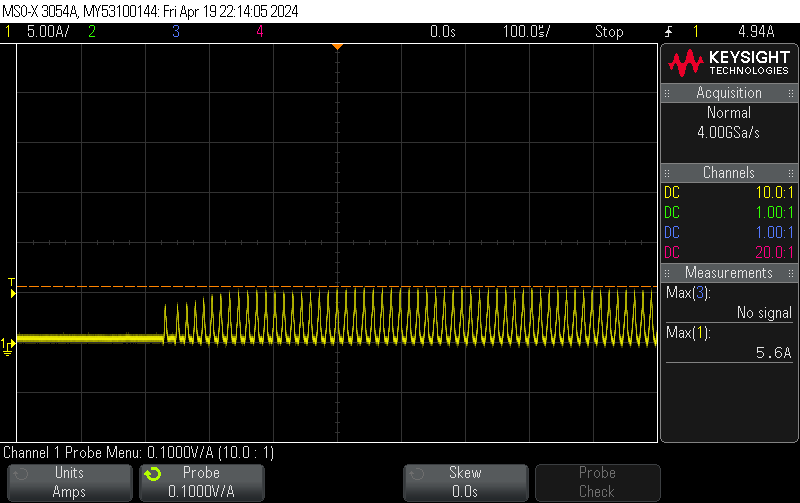

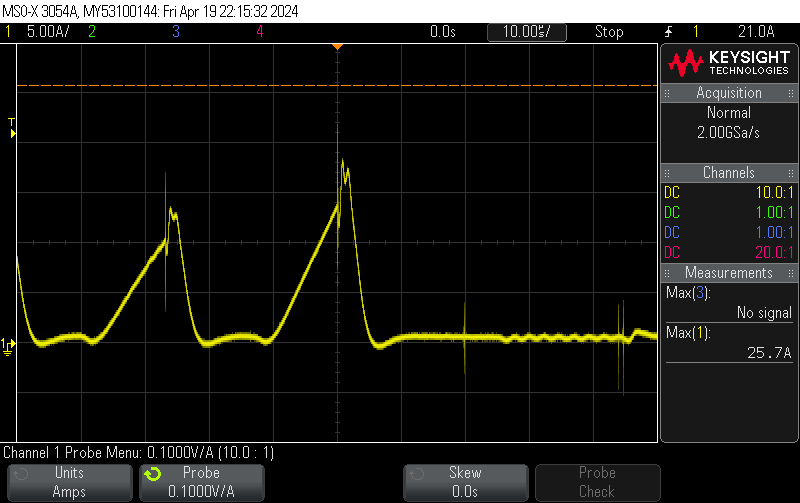

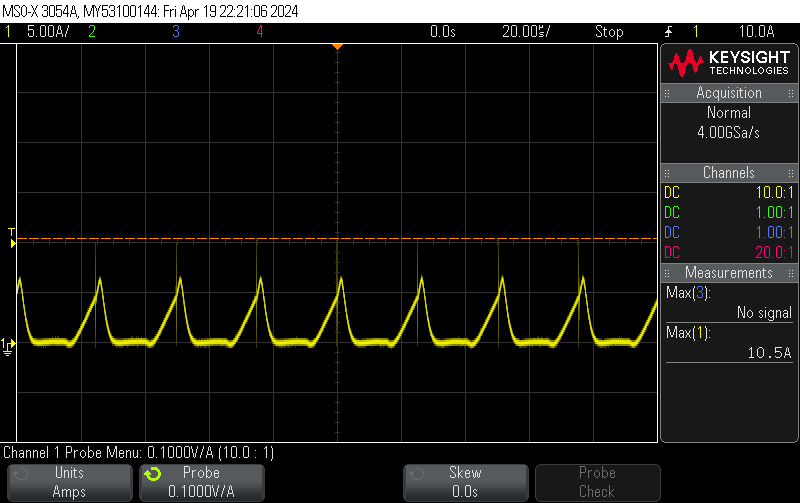

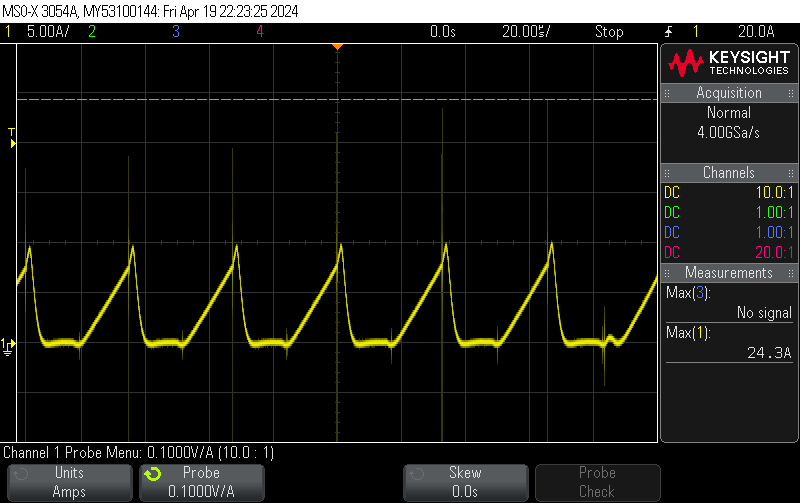

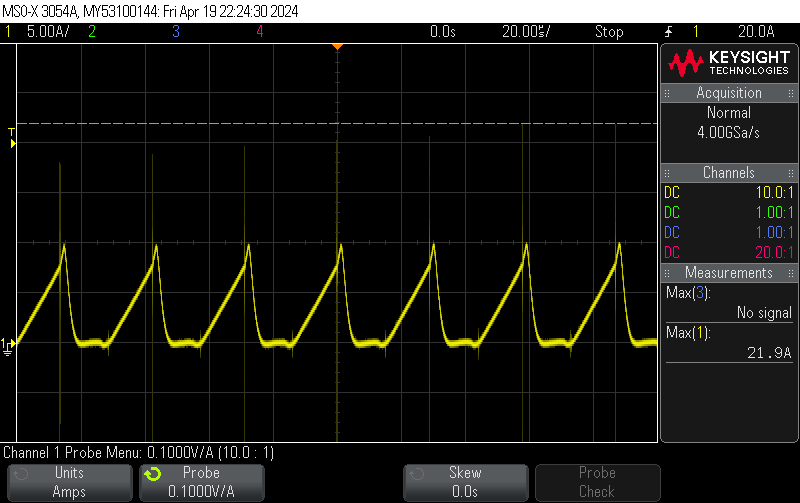

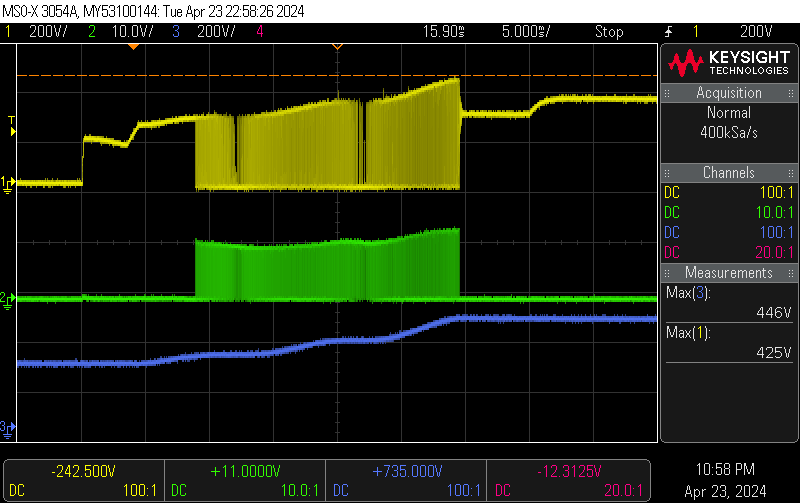

Please see the following measurements:

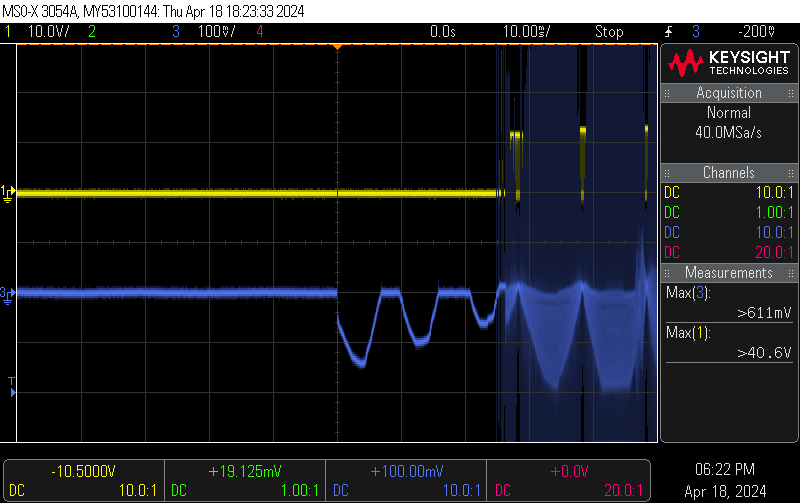

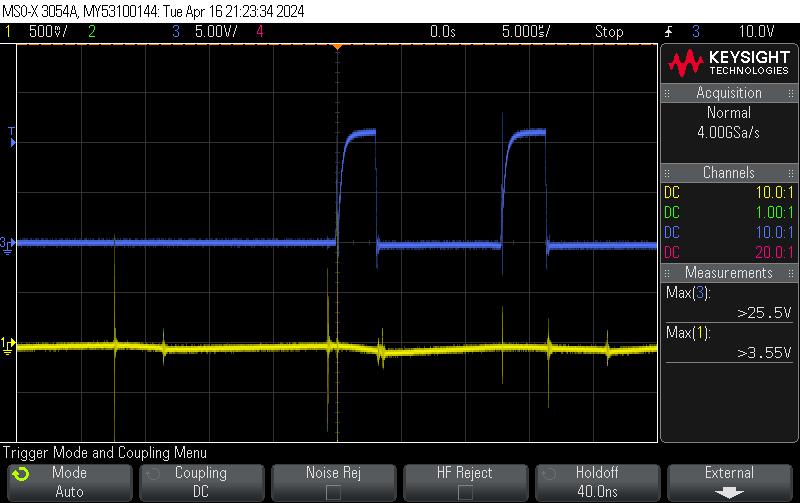

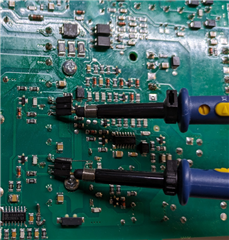

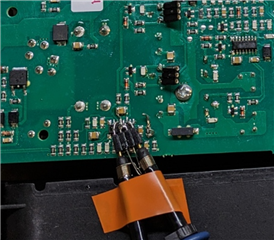

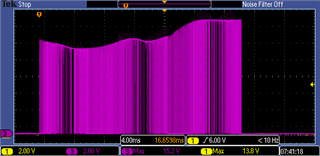

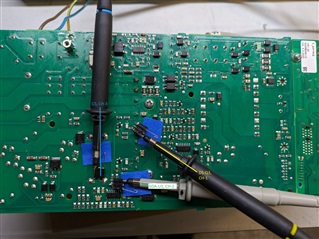

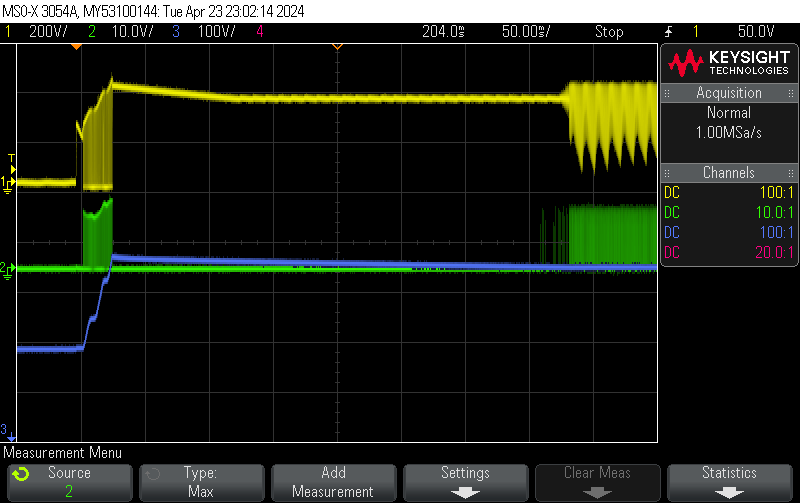

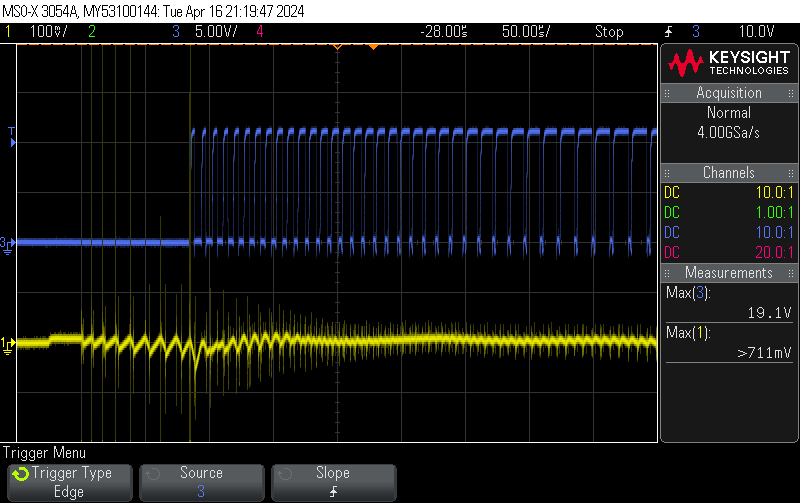

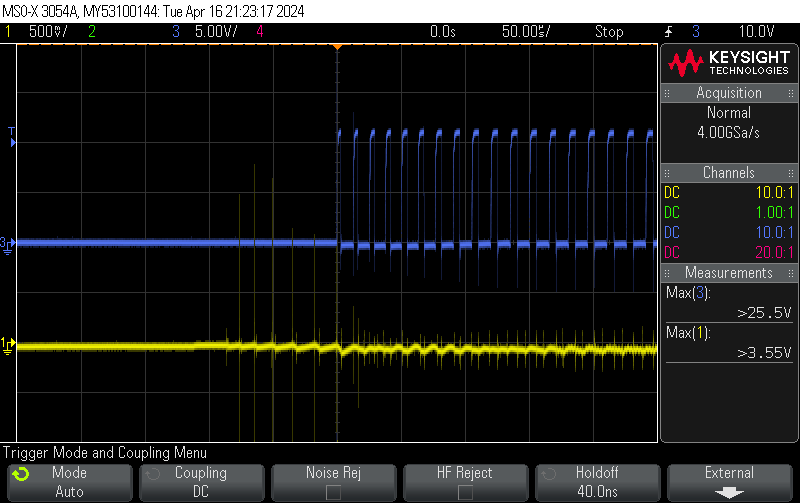

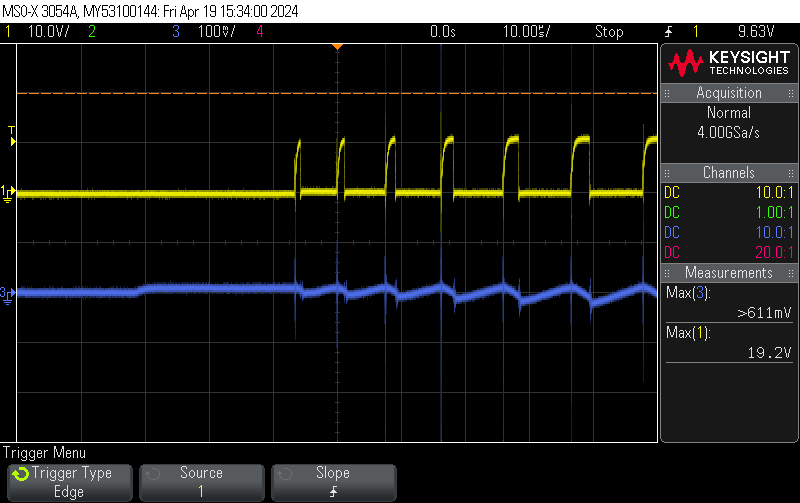

1. Measuring the GDA, GDB pins of U1 at start up (CH-1 GDA, CH-3 GDB)-Input voltage 220V AC:

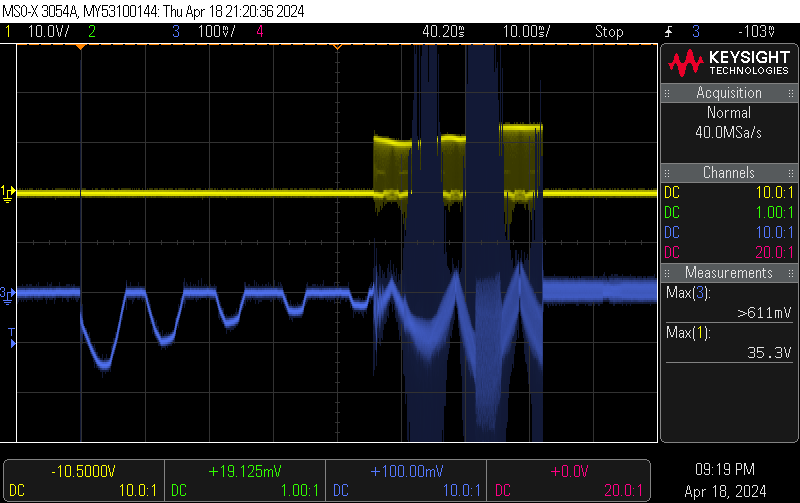

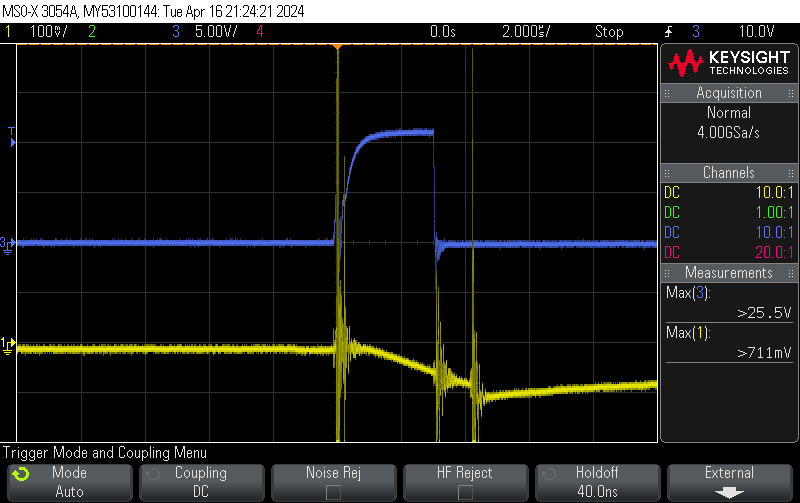

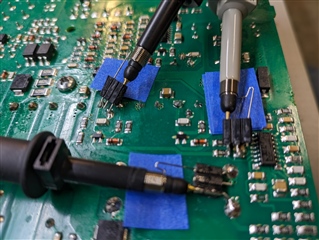

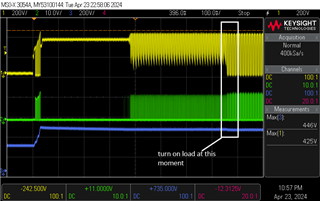

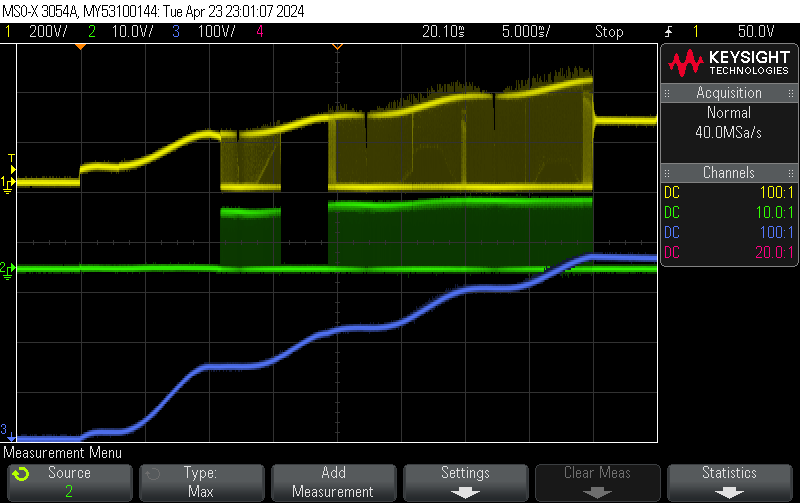

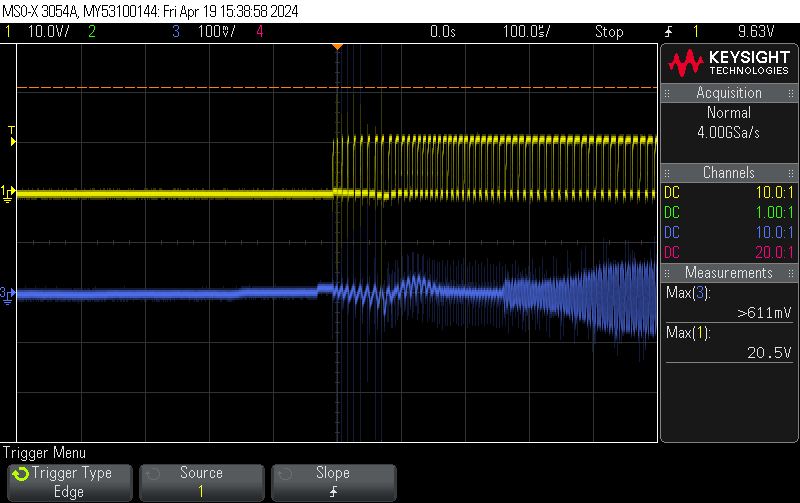

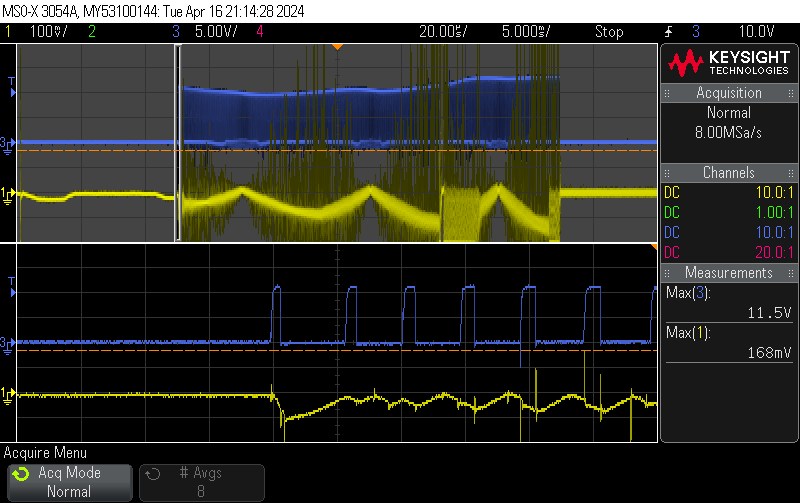

2. Measuring the GS-Q1, GS-Q3 at start up - Input voltage 220V AC:

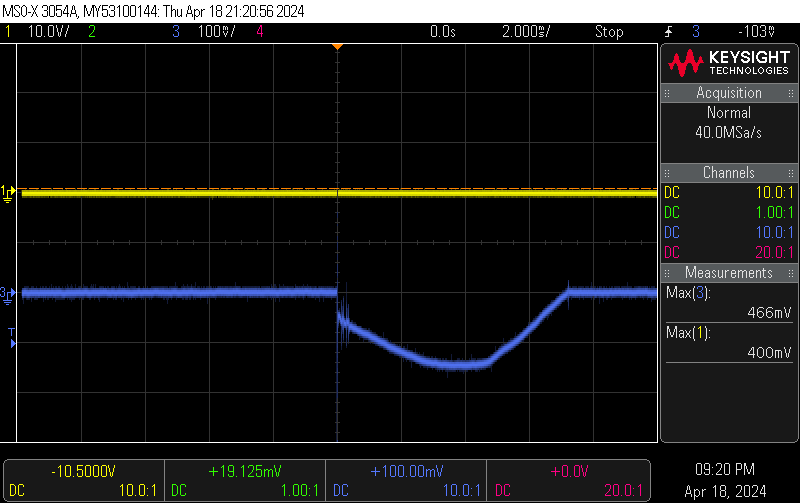

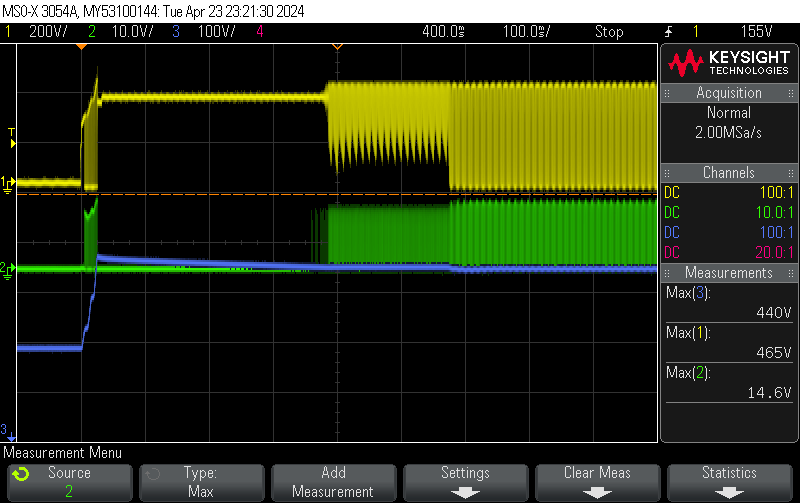

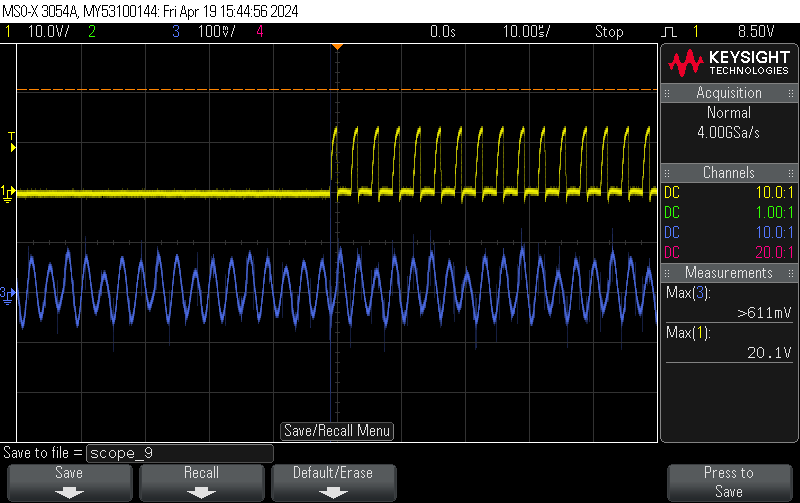

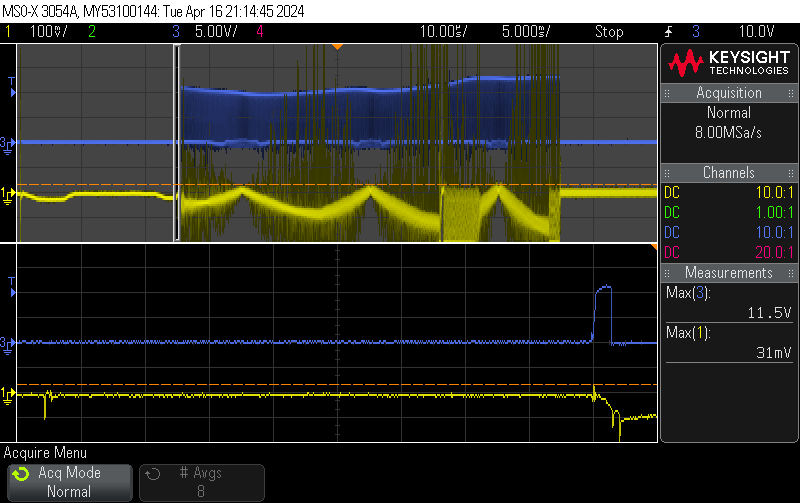

3. Measuring the GS-Q1, GS-Q3 at 200W - Input voltage 220V AC:

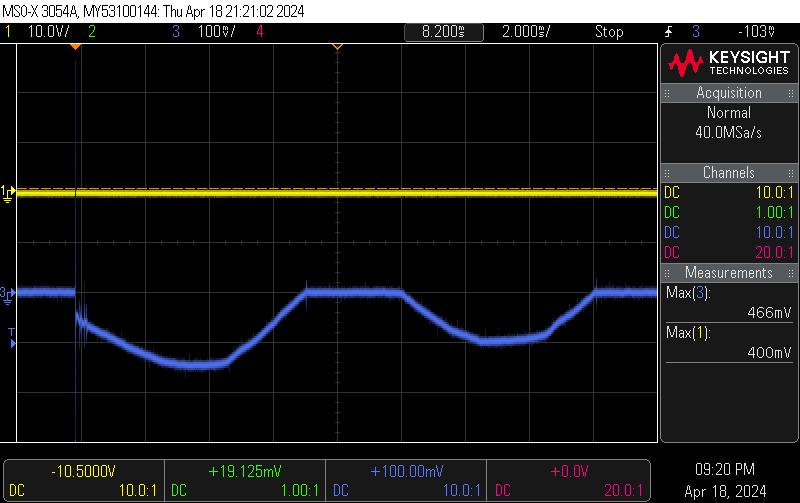

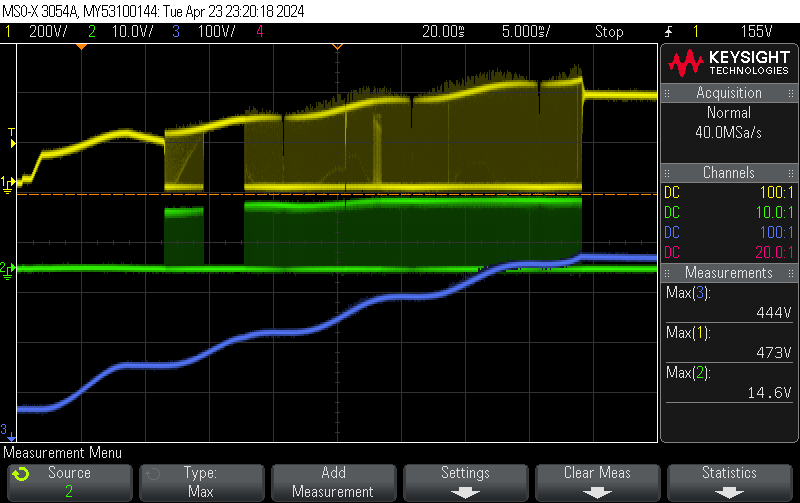

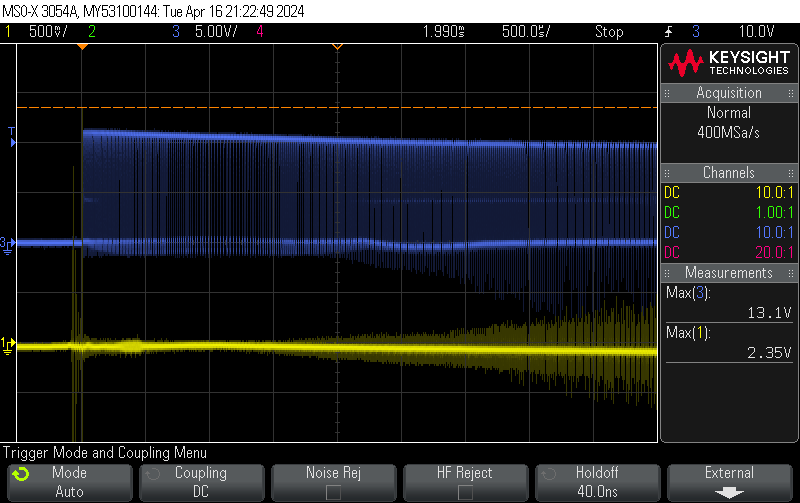

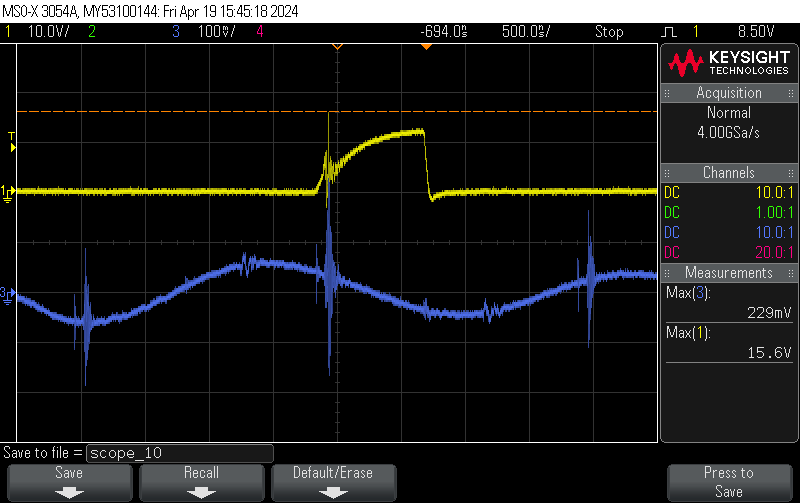

4. Measuring the GS-of CH1 at Startup - input voltage 220V, with better oscilloscope (500MHZ):

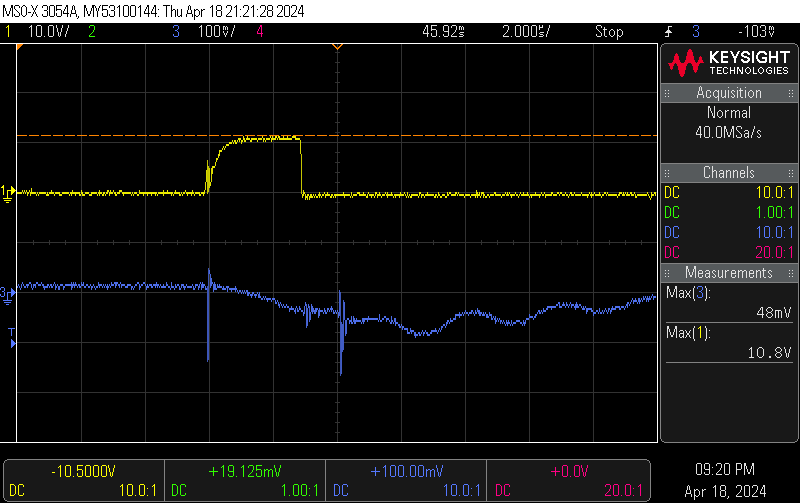

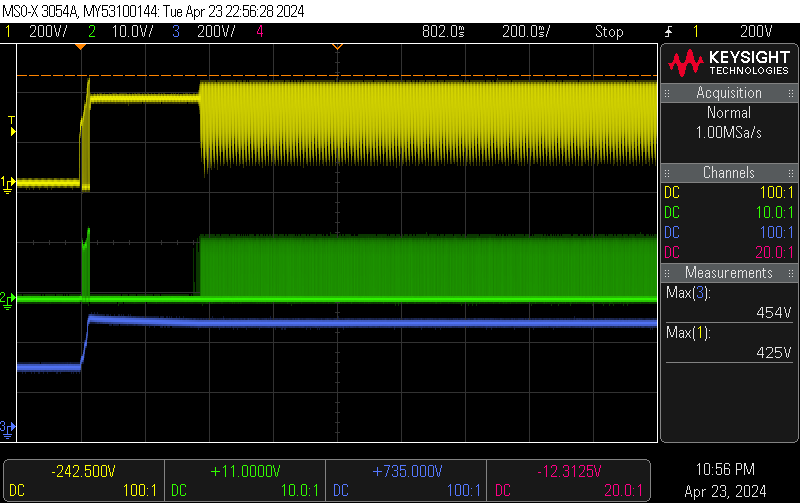

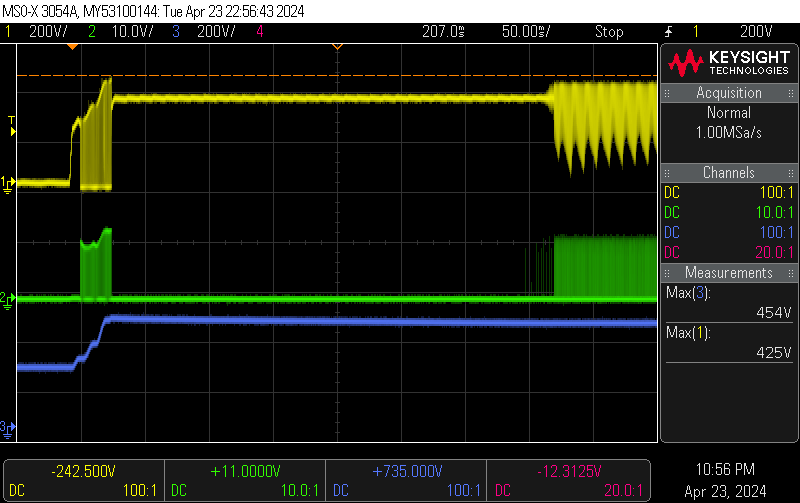

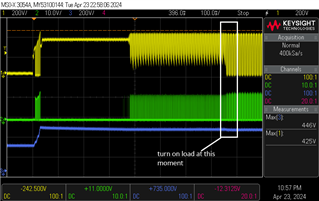

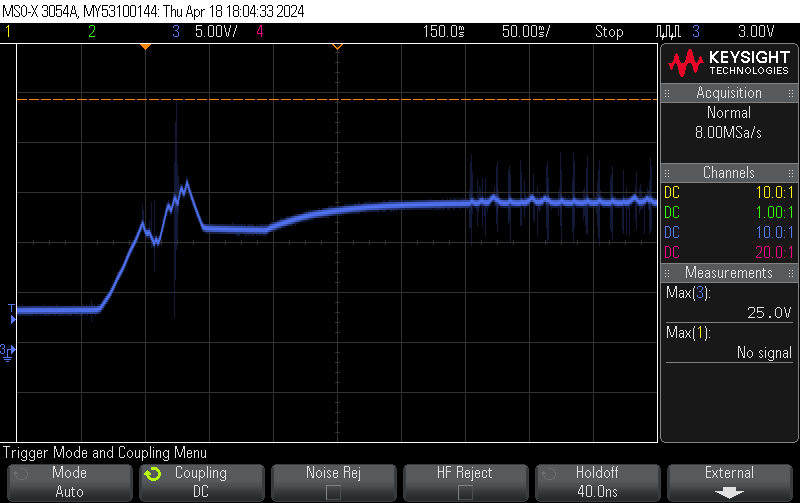

5. Measuring VCC at start-up:

6. Measuring CS pin (U1), GS-Q1 @ 170W (CH-1: GS, CH-3: CS) - Input 220V AC:

7. Measuring CS pin, GS-Q3 start up (CH-1: GS-Q3, CH-3: CS pin) - Input 220V AC: