Our company uses 1 piece of TPS53353 to supply power to two pieces of XC7K325T-2FFG900 nuclear pressure VCCINT1V0 at the same time (accuracy ±3%), the total current demand is expected to be about 15A, there is a huge voltage fluctuation(max:2.4V) in the working process, about a few minutes of occurrence, no specific law was found, what is the reason for this, or what causes such fluctuations, how to solve it?

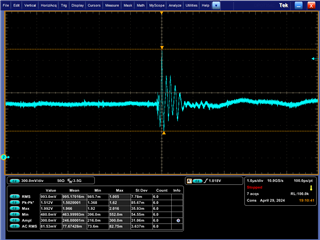

The test waveform is as follows:

The schematic diagram is below:

Best wishes!