Hi,

I intend to use a TPS2663(1) as an efuse with OVP, UVLO and reverse protection on two power rails in my design.

I'm simulating this in PSPICE, but finding that the UVLO does not appear to activate at the desired voltage.

OVP functions correctly.

UVLO does not activate and assert FLT until a much lower voltage than I expect.

OVP activates at 30V and I'd like UVLO to activate at 20V.

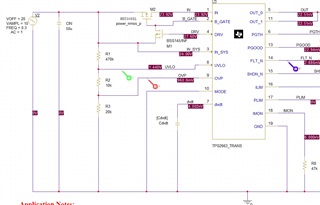

This part of the circuit is shown below.

Values for R1, R2 and R3 are selected based on the datasheet parameters to set UVLO and OVP.

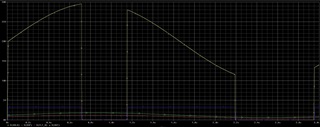

My simulation results show OVP activating correctly around 30V.

UVLO does not trigger until the input (and output) voltages fall below 12V, when the UVLO pin is <800mV (Threshold should be 1.12V falling).

Any idea why this may be the case?

If this is just simulation weirdness that I won't see in the device in real life, I'm happy with that, but I'm also confused why it's happening in the sim!

Any thoughts appreciated.

Thanks in advance!