Other Parts Discussed in Thread: UCC28950

Hello,

Background:

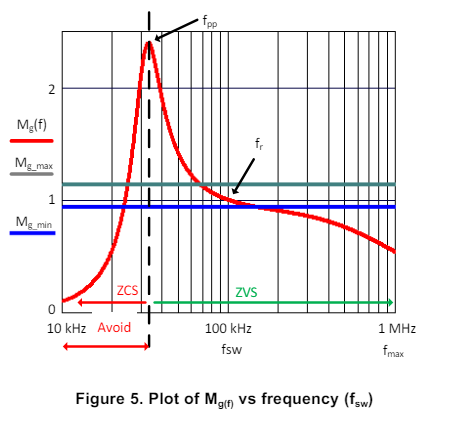

Looking for some design advice in relation to disabling burst mode on the UCC256404. The objective of my LLC convertor is to maintain a 24V output from a 400V input, SWF 90Khz-120Khz with max load 10A. Initial operation in Option mode 6, resulted in burst mode activating in any load condition. After referring to the 7.4.3.2 section within the data sheet, I have programmed the BW pin to allow for Option 7 ( Burst mode disabled). Following this, I proceeded to test the circuit but found with an input of 180V to be losing regulation in the output voltage and the Switching frequency was capped around 60Khz.

Question 1

Is there a way to increase the maximum switching frequency within the Burst mode disabled operation?

Question 2.

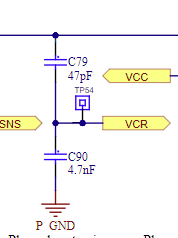

How should the LL/SS pin and the VCR pins be configured when burst mode has been disabled?

Cheers,

Euan