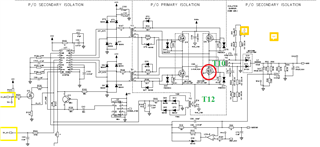

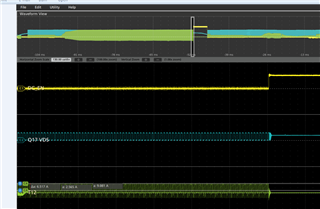

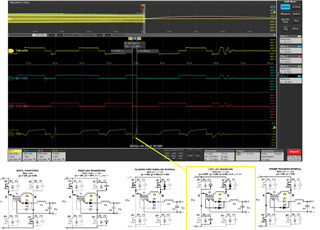

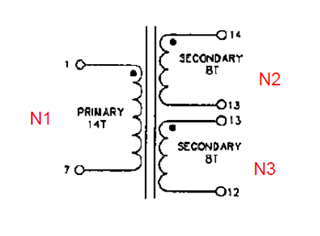

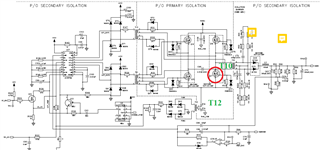

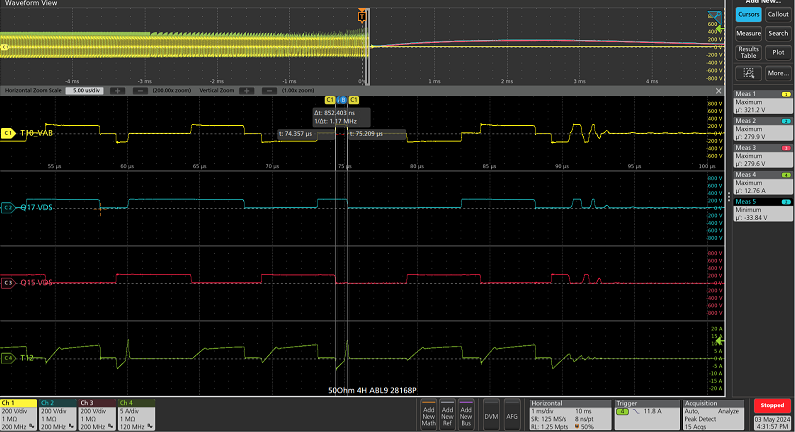

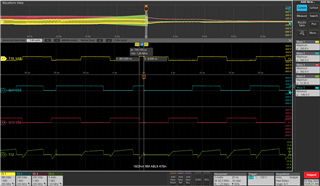

We are experiencing high failure rates for our Q17 (low side FET on the right leg) under close to short circuit conditions. We are observing the cycle-by-cycle current limit phase shifts Q15 (left leg) and begins conflicting with required transfer time between the two legs. Wanted to ask measure we can take to mitigate this issue?