Other Parts Discussed in Thread: TPS40055

Hi,

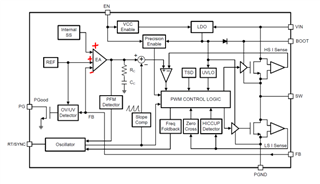

I have a question concerning the FPWM of the LMR38010FSDDAR.

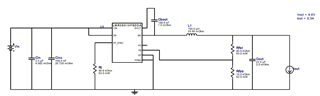

Take a basic circuit with 48V input and 9V output.

In my application it might be that the output is pulled higher than 9V. I thought FPWM would then pass a negative current through the low side FET to maintain the 9V output.

As this does not happen, my question is if I am thinking of it wrong? Or maybe the circuit is wrong? Or Digikey did not supply the F part?

Any help is welcome, thanks in advance!

Regards,

Bert