Other Parts Discussed in Thread: CSD19532Q5B, UCC27714, CSD18540Q5B

Dear TI Team,

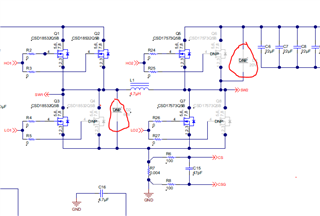

We are using LM5176 for our one of application.

We would like to understand below few queries

1) Could you please clarify us, will the Higher side MOSFET ( HDRV1 Or HDRV2) will continue remain ON ( e.g 100% duty )?

Considering any case e.g boost, buck or any other mode.

2) If yes, how the boot capacitor will charge when upper MOSFET continue (100 %) ON e.g LO remain off?

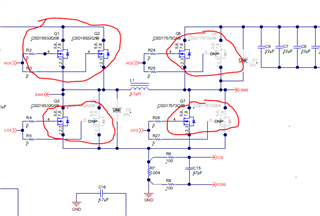

3) Will the LM 5176 can drive parallel MOSFET topology i.e 4 or 5 MOSFETs are in parallel to increase the current capacity.

We are using CSD19532Q5B this MOSFETs for parallel topology.

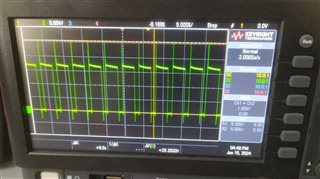

4) Could you please share few waveforms with us as below.

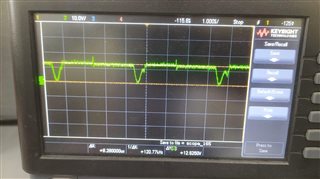

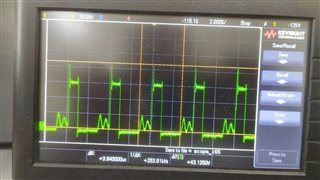

i) HDRV1 & LDRV1 waveform for all modes ( e.g buck, boost any others mode)

ii) HDRV2 & LDRV2 waveform for all modes ( e.g buck, boost any others mode)

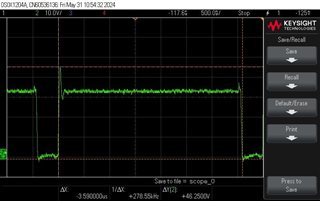

iii) Current sense ( i.e CS and CSG ) waveform for all modes ( e.g buck, boost any others mode).

Note: We checked in EVM details but we haven't found above waveforms in the same, so could you please share the same.

Thank you!