Other Parts Discussed in Thread: TPSM53604, TPSM33625, TLVM23625

Hi,

I'm planning on using TPSM53602RDAR. The datasheet clearly states requirements for both input and output capacitance, output capacitance as a function of output voltage and input capacitance 20uF ceramic.

- What constraints are considered when setting the output capacitance requirement? 42uF is rather huge and one of the main advantages of switching at high frequency like this device is being able to save in passives.

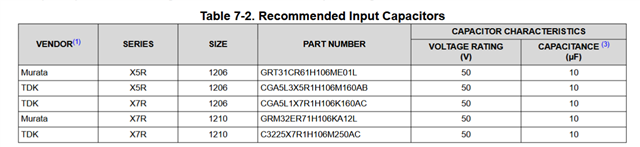

- What constraints are considered when setting the input capacitance requirement? 20uF is rather huge and one of the main advantages of switching at high frequency like this device is being able to save in passives, additionally, in 8.2 Typical apllication, 2x 10uF 50V caps are used, it is not hard to find caps with 80% bias derating at 24V and so it makes me wonder whether the 20uF requirement is to be considered. Often the Cin in a buck converter is set by constraining the maximum input voltage variation, and by knowing fsw, i and C it can be calculated. I also performed a design in Webench and it recommended a total input capacitance after DC bias derating of 11uF.

THanks and regards