Tool/software:

Hi Team,

I want to actually use TPS543B22 in my design.

Vout:1V、Iout:10A

I have some questions I would like to ask

Q1: Regarding the EN Pin, I saw that the maximum voltage is 5.5V, but I accidentally connected 17V and found that it worked normally and the IC was not burned.

I know this design is not correct, but I want to know whether there are protected Diodes inside the EN Pin?

Because I measured the voltage of the EN Pin and found that the EN Pin voltage is maintained at 11.7V, and the same result is obtained when Vin is between 12 and 18V.

Q2: There is an OPA inside the EN Pin. What is the voltage source of this OPA? What is the voltage level of OPA -?

I would like to know if the 11.7V of Q1 is related to the internal OPA?

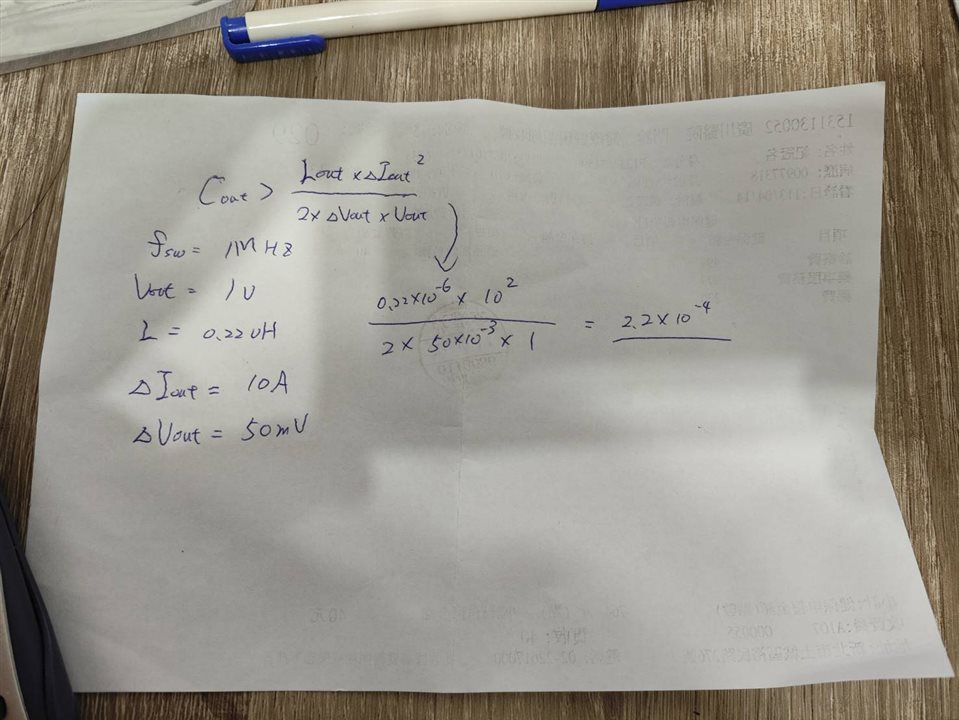

Q3: For the selection of Output Capacitor, I saw that P24. provides four ways to consider Cout.

Which of these are more recommended? Or can I choose any one?

Q4: There is a 10R between SW and FB. I saw that the description of this resistor is a measurement BODE diagram. Is it possible to remove this resistor and would it have any impact on the design?

Q5: On the FB feedback path, CFF and RFBT need to be installed. Refer to the public version of the design RFBT=10K, CFF=68pF. Suppose I modify RFBT=4.99K here, is it feasible to maintain CFF at 68pF?

Is there any formula I can use to verify the stability of this circuit?

Many thanks.