Other Parts Discussed in Thread: AM5716

Tool/software:

Hello, experts.

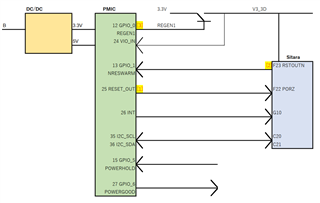

Our set has the following circuit configuration.

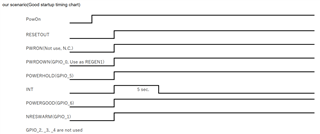

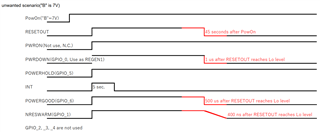

When "B" voltage is 13.2V, PMIC's "RESET_OUT" is High Level.

But "B" voltage is 7V, "RESET_OUT" is going to Lo level after 45 seconds form power on.

Then the output voltage levels of DC/DC(5V and 3.3V) are no probrem.

The output of the PMIC is OK(Each voltage level is OK).

The "PWRGOOD" remains at High level.(I thinki it is OK).

We would like to know why the "RESET_OUT" signal goes to Lo level.

Is it due to commands from the AM5716 (via I2C)?