Tool/software:

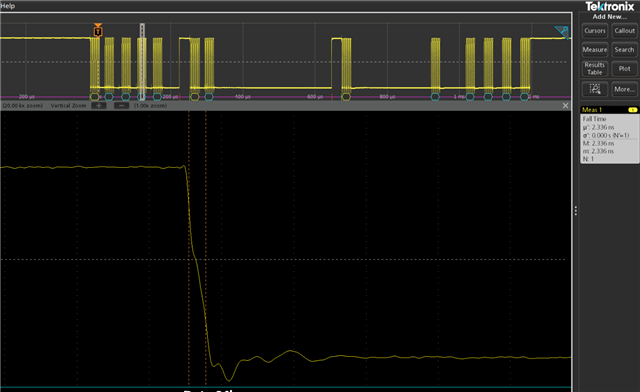

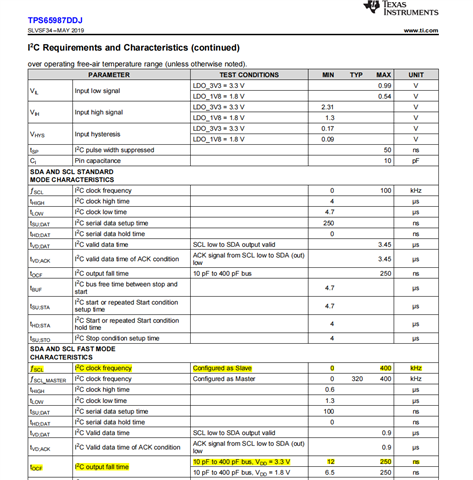

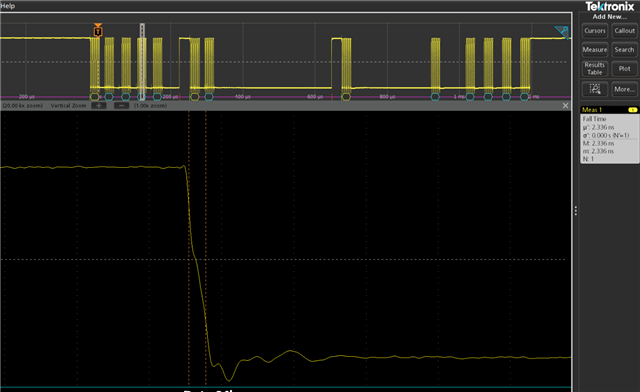

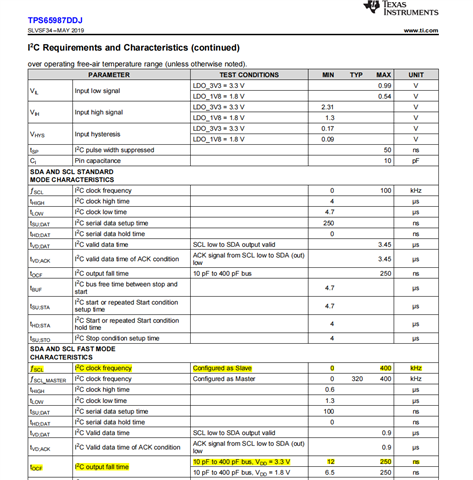

PD chip as slave, the I2C clk frequency is about 349.8 KHz, fall time is measured about 2 ns, while the spec tOCF is 12~250 ns, is that ok for TBT3 dock design?

Attached the screenshot for reference, please have a check, thanks a lot.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

PD chip as slave, the I2C clk frequency is about 349.8 KHz, fall time is measured about 2 ns, while the spec tOCF is 12~250 ns, is that ok for TBT3 dock design?

Attached the screenshot for reference, please have a check, thanks a lot.