Tool/software:

Hello,

I am trying to verify the timing data for the CSD17484F4. I am using the unencrypted Pspice model given for this device in a Cadence Virtuoso testbench. This testbench is meant to replicate the test conditions used within the spec sheet to generate the timing data. Below is a screenshot of my test bench:

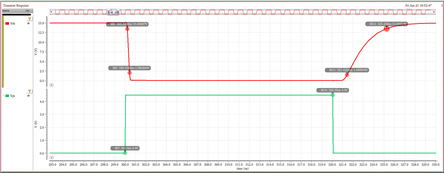

The gate is driven by an ideal square wave voltage source that pulses between 0 and 4.5 V with 50ps rise and fall times. The drain is biased with a 15 V dc source and is paired with a series 30 ohm resistor to limit the drain current to 0.5 A. Below are the results of the transient analysis:

Comparing my results with the numbers given in the spec sheet, I find the following:

| Transient Sim | Spec Sheet | |

| Turnon Delay Time | 200ps | 3ns |

| Rise Time | 200ps | 1ns |

| Turnoff Delay Time | 1ns | 11ns |

| Fall Time | 3.8ns | 4ns |

Can someone please help me understand why my testbench is much faster than the data given in the spec sheet? Should I expect the MOSFET to perform more closely to my modeled results or the spec sheet results?

Thank you for your time,

Braden