Tool/software:

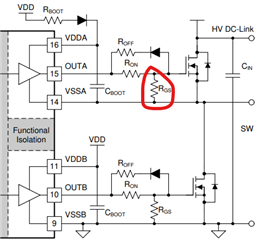

Each UCC21222D chip drives the half-bridge consisting of P-channel (high side) and N-channel (low side) MOSFETs. Unfortunately due to a problem in the logic, sometimes we get simultaneous positive pulses on both inputs. We are working to find and fix this problem but meantime for awhile our last hope for the prevention of a shoot through is this feature of the chip to prevent simultaneous outputs and also a dead time setup. Dead time set to ~ 1uS by 100kOhm resistor. We have both output channels powered by the same 12V source bypassed by two caps 0.1uF and 4.7uF . There is chance that there is a short glitch - drop in this 12V output driving source but so far oscilloscope has not caught such drop.

Yet, MOSFETs are getting burned when input active pulses arrive simultaneously. What could be wrong? Why the chip does not prevent simultaneous outputs? Is there errata on this driver chip ?

Please help.