Other Parts Discussed in Thread: LMV431

Tool/software:

Hi TI Team,

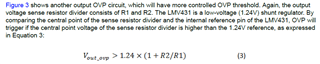

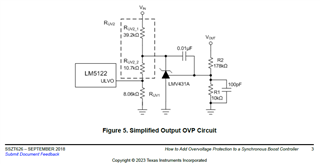

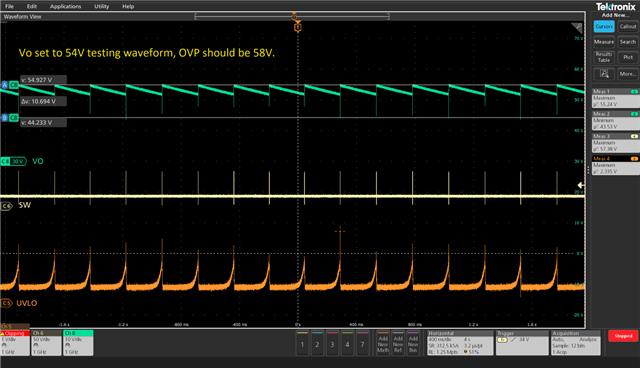

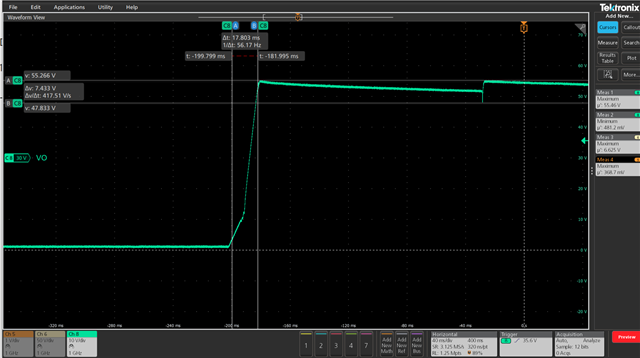

I follow TI's circuit and apply in our design for Over Voltage protection, in Vout=54V application, R1=10k (PR191), R2=453K (PR192), OVP setting point should be 57.412V (Eq.3)

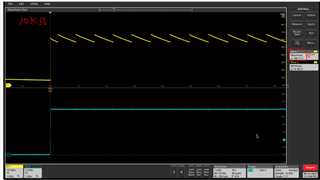

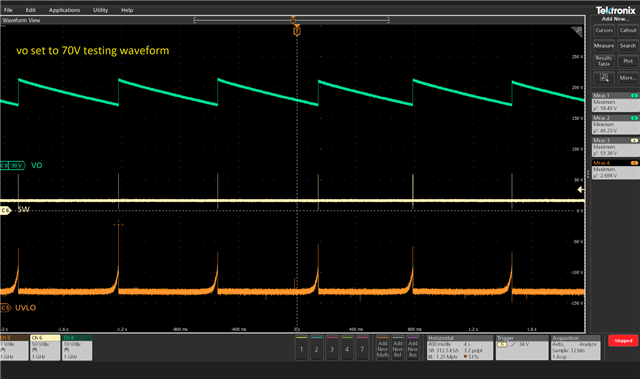

In real test, why the Vout clamp in 68.11V?

Since our OVP target is clamp Vout<60V, I try to modify PR191 from 10k to 12k, although the OVP could clamp in 59.66V, but this modification already impact the normal operation.

How to sett he OVP <60V, and won't impact the normal operation as well? Please help to clarify this issue, thanks!