Tool/software:

Hello,

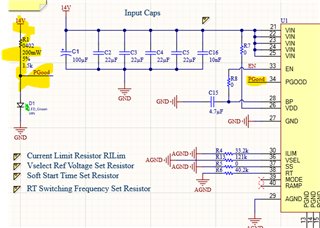

I'm making sure the way I am setting up PGOOD doesn't stress the drain on the FET controlling the output logic on PGOOD.

If PGOOD is low the FET should pull PGOOD node to ground sinking 9.5mA through a 1.5k resistor connected to 14v. If PGOOD is high then the drain is open and sees Vforward bias on the LED indicator light in the circuit shown.

I know we used this circuit on another device and it broke the PGOOD pin I believe because it had a lower voltage rating than 14v. I don't expect 14v to actually be on the pin, but I guess it could happen as well.

Please, let me know if there is a smarter way to do this or if this seems like a good way to go.

Thank you,

Matt