Other Parts Discussed in Thread: LMR54410

Tool/software:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Peter,

Thank you for providing the details of your problem. I just had a couple of comments on your application:

Thank you,

Joshua Austria

Thanks Joshua for your quick reply. Please see my replies below:

Noted.

D1 = Toshiba p/n CMS06. It's rated for 2A.

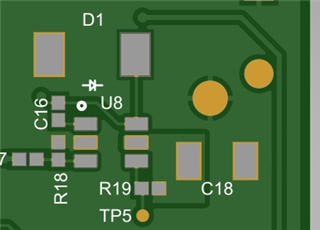

Top:

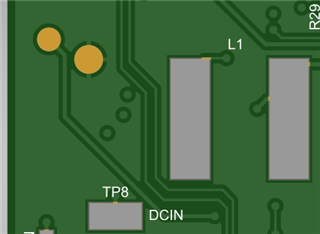

Bottom:

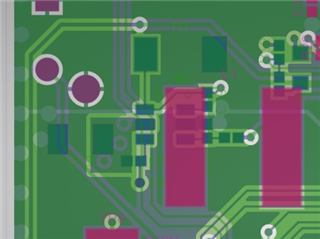

Stack (ground and power planes in the middle):

~10-60 degC for the units we pulled in from the field -- it's an outdoor application, so ambient temp can vary widely.

Not that we know of. The batteries are non-rechargeable, starting at 14.4V when fresh and going down from there. Occasional high-current demands on the battery cause its voltage to drop by 1-2 V, but it recovers quickly, and without spiking. Neither the battery nor the circuit have a low voltage cutoff.

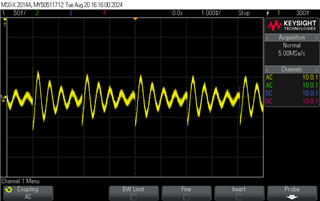

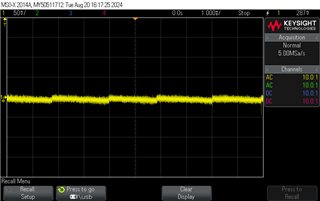

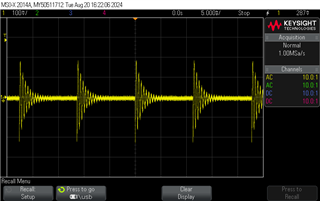

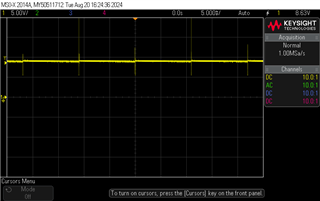

Bad Vin:

Bad Vout:

Bad SW:

Bad CB:

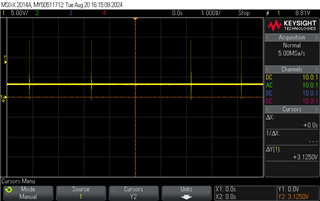

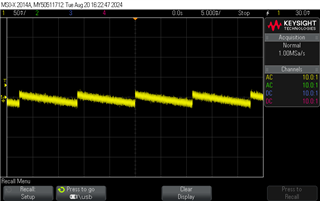

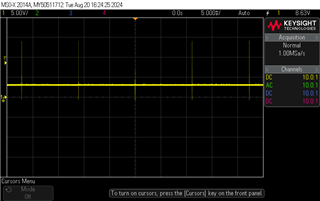

Good Vin:

Good Vout:

Good SW:

Good CB:

Notes:

--Waveforms are from the two EVMs that I mentioned, with the following modifications from stock:

R4 = 64.9k

R3 = 19.6k

L1 = 120uH (Wurth p/n 74404084121)

R1 = 10k

R2 = removed.

--Please note the different timescales for the good (= 5 ms / div) and bad (= 1 ms / div) waveforms.

Thanks.

Hi Peter,

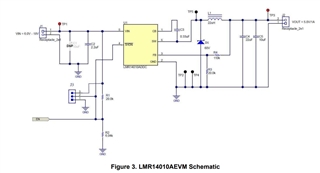

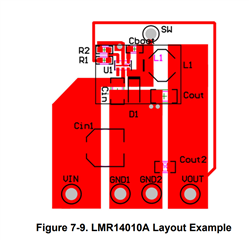

It looks like there is not something necessarily wrong with your schematic, but your layout is of some concern. Following the layout guidelines in section 7.4 of the datasheet is critical to ensuring that your device operates as expected. Prolonged operation of the device in a sub-optimal layout can cause damage to the device and/or harm its performance. I reviewed your layout, here are my comments:

For more details, please see section 7.4 of the datasheet.

Thank you,

Joshua Austria

Thanks Joshua. Yes, the layout is definitely sub-optimal. Unfortunately it's a legacy design, and the original designer didn't take much care with the layout of this and some of the other subcircuits...

But, I wouldn't expect a bad layout to permanently damage / degrade the LMR14010A -- which is what we're seeing, because the old chips continue to underperform after being moved over to an eval board (which presumably has a good layout). And, in any case, we're also stuck with the bad layout for a while, on our existing devices.

So:

1. Are there any more tests we can do here to determine the root cause of the LMR14010A issue?

2. Can TI take a look at some of the parts we've pulled from the field? (if so, please let me know how to arrange for that)

3. Are there any pcb reworks and/or component changes that we can proactively make to our existing devices to prevent the issue from recurring?

4. Is there any benefit to replacing the LMR14010A on existing devices to LMR54410?

thanks,

Peter

Hi Peter,

In my experience, layout does have the potential to permanently affect the device's performance as it could subject the device to stress that is not expected from a device in a normal operation. TI does not guarantee the performance of the datasheet for devices that are not in compliance with the datasheet recommendations. That being said, I see your conundrum and while I still stress that changing the layout is important, I will answer your questions:

Overall, I believe that the best advice that TI can give is to change the layout to be more in-line with the datasheet recommendations. If this is done and the part is not operating above the maximum ratings provided in the datasheet, the part should perform as expected.

Thank you,

Joshua Austria