Tool/software:

Dear TI experts,

My customer considers TPS22811 for specific purpose.

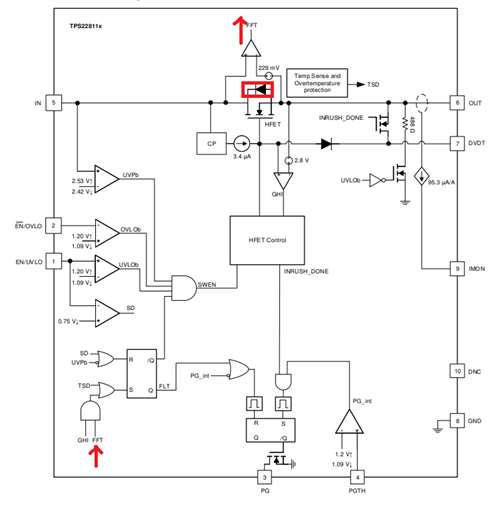

They chek the step as follows, based on block diaram of TPS22811.

1. Apply 12V to output, and leave input floating.

2. FFT signal is activated due to voltage drop of body diode of HFET.

3. PG pin is reset.

4. Using this PG low signal to control other IC. (EN pin low)

(They added 200~400ohm resistor between input pin and GND to make large voltage drop of body diode of HFET, make 30~60mA current as a result.)

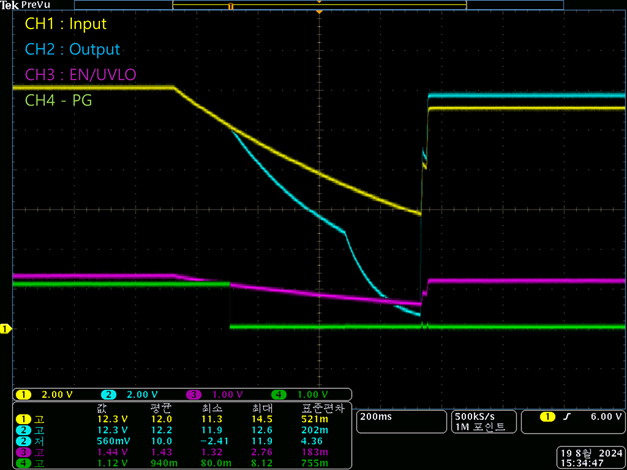

At first they checked that voltage difference between input and output pin is enough, so PG pin is pulled to low as they expected.

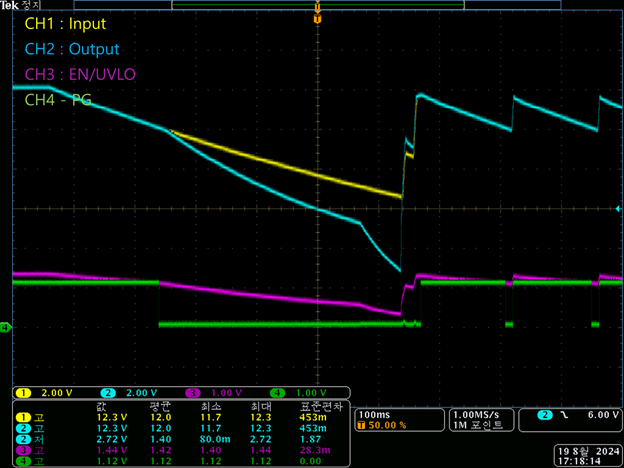

But some time passed, waveform changed a little as below and PG pin is not pulled to low.

They expect that body diode of HFET is broken so the voltage difference is not made to PG pin low.

- Here are my questions ;

1. I want to confirm that the sequences of my customer (1. to 4.) make sense or not.

2. Is it right to use FFT signal to control PG pin?

I can find onlt the relationship between PG in and PGTH, but nothing else.

3. They need to use strong pullup for PG pin to control external IC. (need to make 5mA or higher current)

But datasheet says that strong pullup yields just 242uA current. Can my customer us stronger pullup?

Please check these issues. Thanks.

Best regards,

Chase