Tool/software:

Hi Sir,

may help double confirm this layout is ok?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Tommy,

Yes we can support layout review. Could you share a .brd or a .PcbDoc layout file?

Best regards,

Diang

Hi Diang,

In the attachment, please find the .brd file we converted from .pcb.

Maybe a little different from the original .pcb archive, but I think it's pretty much the same as the .pcb archive.

Please help review it. Thanks!

Best regards,

Ian

DAP-X3060W_MB_20240905-poe.brd

Hi Ian,

Thanks for the PCB document. I should be able to get back to you by next week.

Best regards,

Diang

Hi Ian,

Thanks for your information. I will prioritize this work and get back to you by next Tuesday.

Best regards,

Diang

Hi Ian,

Thanks for your patience. Please see the comments below:

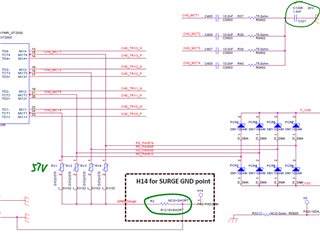

1. I may not be familiar with this application, just curious if it is ok that when R2 is mounted, your circuit will have 57-V rated surge varistors in parallel with Bob-smith termination with 2-kV rated isolation. In this case, the isolation voltage will be degraded. Then the 802.3bt isolation requirement may not be met.

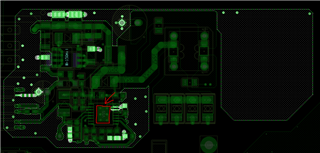

2. It is recommended to make the GND_EARTH not crossing the PoE wires. Better to make a clear boundary with proper insolation distance.

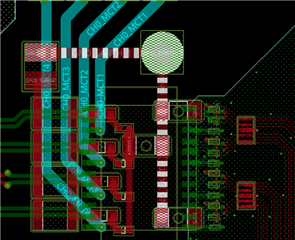

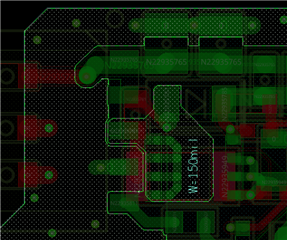

3. The polygon of Vneg in inner layer covers some through holes. TPS23751’s pad also has concerns.

4. The distance between primary side FET and Vneg are too close. Please consider increase distance to >0.6m to ensure sufficient clearance distance and reduce noise coupling.

Best regards,

Diang