- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi, TPS3840 support team

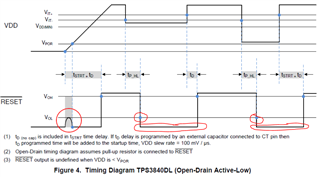

The undefined pulse occurs at VDD power up as shown in following figure. And the voltage on /RESET pin looks like to clamp to VOL.

Is it really clamped to VOL ? If there are a possibility for the undefined pulse to over VLO, what voltage can you assume it will be clamped up to?

Thanks

Tamio

Hi Tamio,

Sorry the timing diagram is not drawn to scale. The VOL line indicate the highest point that the LOW signal can go and not indicate the maximum Vpor spike of the RESET.

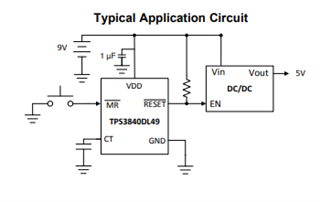

As for the maximum value of the spike, for standard schematic as shown below, it is going to equal the VPOR value as maximum.

Jesse

Hi. Jesse,

Thank you for your prompt reply.

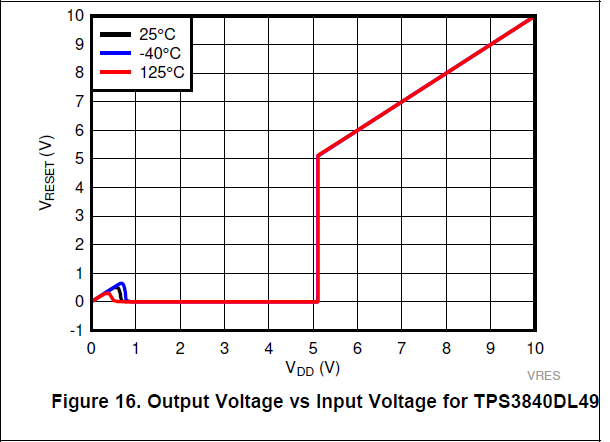

I understood that the peak voltage of the undefined pulse is up to 950mV, which is the maximum POR.

And the voltage on /RESET pin will be tracking with VDD until POR is detected as below

Thanks

Tamio