Other Parts Discussed in Thread: TPS389006

Tool/software:

Hi Team,

Could you help answer below questions regard TPS38700?

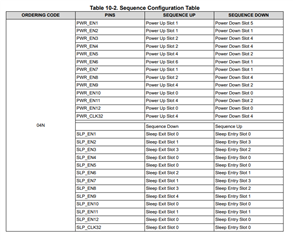

1. Can TPS38700 still have consistent output during the upgrade process?

2.What gonna happened when TPS38700 upgrade failed?

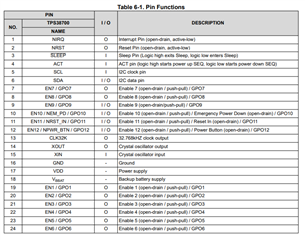

3.What is the IO status of TPS38700 during upgrade?

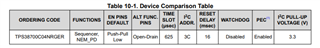

4.What is the default timing of TPS38700

5.Do we have any other new sequencer that can promote to customer?

Thank you,

Yishan Chen