Tool/software:

Hello TI support

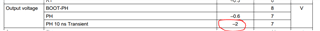

I've got an issue to meet the specification of the PH pin of the TPS54519, especially the "undershoot" as following:

The max abs rating is -2V during 10ns.

My converter operates from 3.5V to 0.95V 5A and has the following undershoot:

CH4 : total output currrent (250mA is not included in this trace)

CH2 : output voltage (AC coupled)

CH1 : PH pin

(min with stat = -2.95V).

The probing is made with a 1GHz scope, 500MHz passive 1:10 probe with a small pigtail (for the GND connection).

The layout is the same as the EVM.

The only way to achieve the specification with margin is to add:

- A RBOOT of 33Ohm

- a high and low side snubber of 2.2Ohm and 2.2nF

(min with stat = -1.64V).

Could you confirm :

- the undershoot measured (with no snubber) is really an issue regarding the max abs ratings ?

- the way to fix it is correct and sufficient ?

The layout and schematics could be provided by email for more detail.

Thanks for your support