Other Parts Discussed in Thread: TPS3430

Tool/software:

Hello

we are using this TPS3430 as windows watchdog with CYT2B74 MCU(5V),

but whenever we connect the debugger/ winades tool at the JTAG_RESET connector for debugging or data capture. Then the Randomly the WDO getting reset.

below you can see the schematic of watchdog section, here the JTAG_REST is connected to DAP connector, and RESET singal is connected to CYTB MCU reset pin.

with and without 120ohm same reset happens and also we tried by replacing the WDO pullup to 30K to make the current less than of 200uA, but still same issue.

2nd option we made little modification on the resistor connection like below, but still random reset happens at flashing or when connected the external tools on JTAG_REST

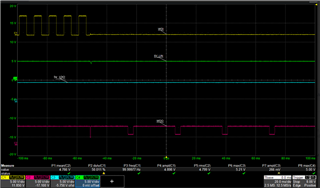

WDI we giving as 100Hz pulses

as per datasheet data seems our design is within the watchdog boundary

please look on the schematic and suggest what is wrong on it what to modify.

Looking forward to your answer as its priority testing.

Thank you!