Other Parts Discussed in Thread: TPS65987

Tool/software:

Hi there—we received an RMA in which the customer reported the device charged very slowly after the charger was inserted following a dead-battery condition.

During boot, our system firmware reads the MODE register of the TPS25750 (0x03) to ensure it matches one of 'APP ', 'BOOT' or 'PTCH'. Looking at the internal logs for this device, the MODE register returned something else in this particular instance. Our system firmware then assumed the TPS25750 was in an error state, and forwent loading a patch bundle. Charging was then limited to 5 V, which explains the customer symptom.

Unfortunately, our system firmware at the time did not log the actual return value of the MODE register, only that it did not match one of the three expected values. I set up an automated test that simulates charger insertion following a dead-battery condition, then checks that the TPS25750 was recognized by our system firmware.

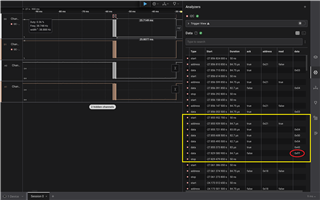

After roughly 5000 trials, I was able to reproduce this issue. In the failure case, the MODE register returned 0x04, 0x50, 0x54, 0xFF, 0xFF (P-T-ÿ-ÿ) instead of 0x04, 0x50, 0x54, 0x43, 0x48 (PTCH). I didn't have a logic analyzer connected at the time, but our logs show that the I2C controller indicated the read was successful.

I suspect the TPS25750 went into a reset state after the read operation already started. With our I2C controller already having received an ACK and nothing to pull SDA low, our I2C controller simply saw the idle SDA line as all ones (0xFF) for the remaining length of the read operation.

My hypothesis is that a glitch on VBUS may have reset the TPS25750 while it was in dead-battery mode and bus powered. To protect against this scenario in the future, we have added a small retry loop to our system firmware. Only if the MODE register consistently returns an unrecognized value, or the read operation consistently fails, will the TPS25750 be assumed to be in an error state. My questions are as follows:

[1] What is the maximum time from VBUS first appearing, to when the TPS25750 can be accessed over I2C and the MODE register will return 'BOOT' or 'PTCH'? This start-up time will inform the delay of the retry loop.

[2] Are there any other explanations or known behaviors that may explain this issue? I found a thread in which a TPS65987 customer observed the byte count of registers read over I2C was correct (e.g. 0x04), but the data bytes also returned 0xFF.

Thank you in advance—in case I can provide any additional information, please let me know.