Other Parts Discussed in Thread: TPS25981

Tool/software:

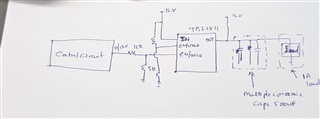

I am using TPS22811 in our design for 12V application. We have around 500uF capacitance on the output of TPS22811. If I just pull high the EN_OVLO pin for power cycling the IC is not turning ON again.

I cannot see any current spikes during re-turn on or voltage spikes at the output. May I know why this is happening ?

Also what would happen if I have more than 500uF capacitance on the output. At any stage it falls into latch ? If so why ?