Other Parts Discussed in Thread: UCD3138FW-BIDI, UCD3138,

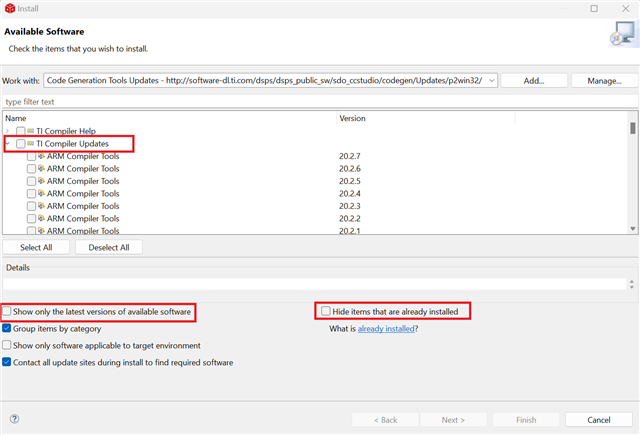

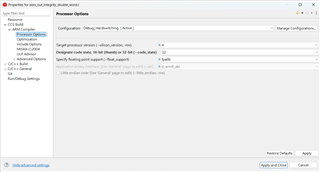

Tool/software:

Dear TI Experts,

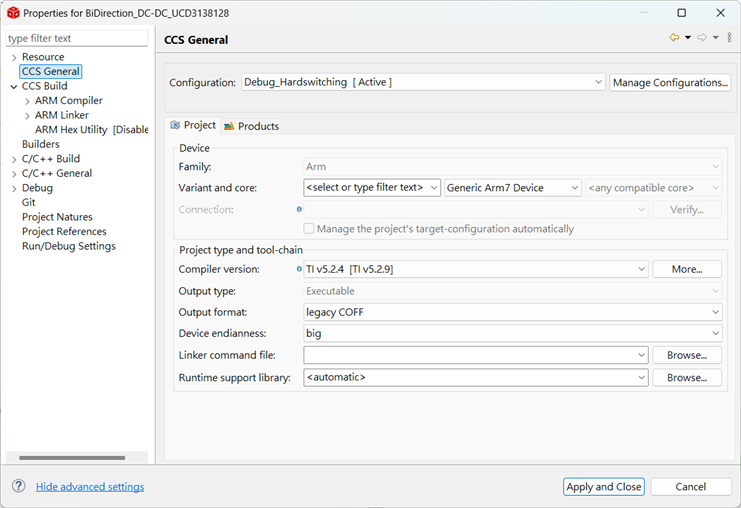

Reference project: UCD3138FW-BIDI

The current project is based on modifying the example firmware, and the intended control actions have been successfully implemented.

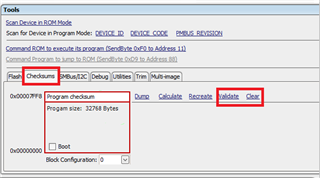

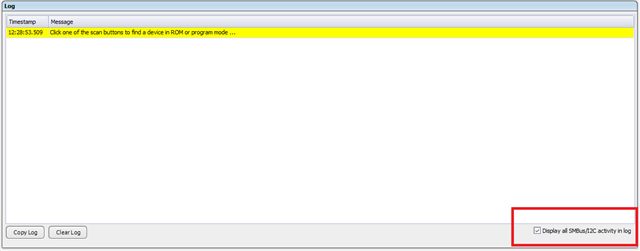

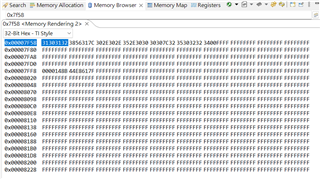

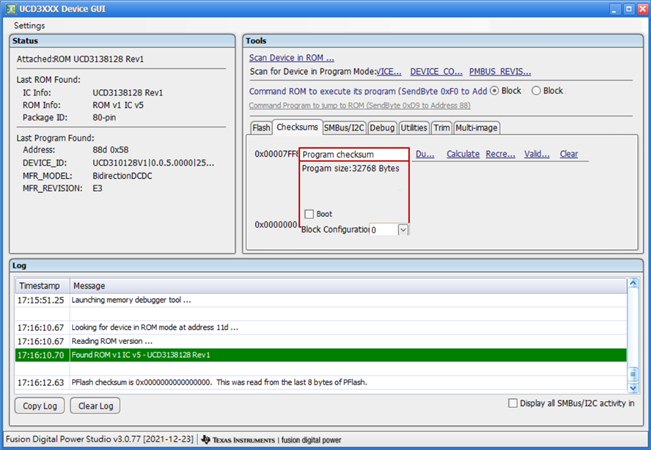

However, when I attempt to use "WRITE program checksum" to program the PFLASH (following the flashing procedure described in the attached documentation), the checksum cannot be cleared when trying to switch back from PFLASH to ROM mode. As a result, the system remains in PFLASH mode. At this point, PMBus communication is functional, and the system operates normally, leading me to suspect that the "checksum clearing" operation was not fully executed.

Current workaround: Using JTAG to manually clear the flash. However, this is not the best solution.

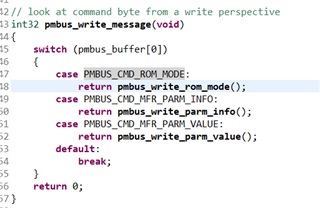

Since the original firmware includes the zero_out_integrity_double_word() function, why is it not executed properly?

Bidirection DCDC Converter User Guide.pdf

Clicking "Jump to ROM" does not clear the checksum, and it remains in PFLASH mode.

software_interrupt ,case 12:

#pragma INTERRUPT(software_interrupt,SWI)

#pragma CODE_STATE(software_interrupt, 32) // this will ensure that this code builds in ARM mode

void software_interrupt(Uint32 arg1, Uint32 arg2, Uint32 arg3, Uint8 swi_number)

case 12: // clear integrity words, depending on arg1

#if (UCD3138128)

//Note: This clear integrity word covers all cases. It is designed to clear integrity words based on what address the flash block is

//mapped to when it is called. This is done for code which switches blocks. And it can erase the integrity word at the end of each of 4 blocks.

//

//For most applications, it can be simplified considerably if code space is scarce

//

//

{

register Uint32 * program_index = (Uint32 *) program_area; //store destination address for program

register Uint32 * source_index = (Uint32 *) zero_out_integrity_double_word; //Used for source address of PFLASH;

register Uint32 counter;

if(arg1 == 0) //0 means first block in memory, regardless of which block that is;

{

zoiw_address = 0x7ff8;

if((DecRegs.MFBALR1.bit.ADDRESS == 0) && (DecRegs.MFBAHR1.bit.ADDRESS == 0)) //here if flash block 0 is at 0

{

zoiw_flash_key = PROGRAM_FLASH0_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR17.bit.ADDRESS == 0) && (DecRegs.MFBAHR17.bit.ADDRESS == 0))//if it's program flash 1;

{

zoiw_flash_key = PROGRAM_FLASH1_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR18.bit.ADDRESS == 0) && (DecRegs.MFBAHR18.bit.ADDRESS == 0))//if it's program flash 2;

{

zoiw_flash_key = PROGRAM_FLASH2_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR19.bit.ADDRESS == 0) && (DecRegs.MFBAHR19.bit.ADDRESS == 0))//if it's program flash 3;

{

zoiw_flash_key = PROGRAM_FLASH3_INTERLOCK_KEY;

}

else

{

return;

}

}

else if(arg1 == 1)//1 means end of second block;

{

zoiw_address = 0xfff8;

if((DecRegs.MFBALR1.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR1.bit.ADDRESS == 0)) //here if flash block 0 is at 0x8000

//note that the address bits start at bit 10, so 0x20 in the address field equals 0x8000

{

zoiw_flash_key = PROGRAM_FLASH0_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR17.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR17.bit.ADDRESS == 0))//if it's program flash 1;

{

zoiw_flash_key = PROGRAM_FLASH1_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR18.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR18.bit.ADDRESS == 0))//if it's program flash 2;

{

zoiw_flash_key = PROGRAM_FLASH2_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR19.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR19.bit.ADDRESS == 0))//if it's program flash 3;

{

zoiw_flash_key = PROGRAM_FLASH3_INTERLOCK_KEY;

}

else

{

return;

}

}

else if(arg1 == 2) //2 means end of third block in memory, regardless of which block that is;

{

zoiw_address = 0x17ff8;

if((DecRegs.MFBALR1.bit.ADDRESS == 0) && (DecRegs.MFBAHR1.bit.ADDRESS == 1)) //here if flash block 0 is at 0x10000

{

zoiw_flash_key = PROGRAM_FLASH0_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR17.bit.ADDRESS == 0) && (DecRegs.MFBAHR17.bit.ADDRESS == 1))//if it's program flash 1;

{

zoiw_flash_key = PROGRAM_FLASH1_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR18.bit.ADDRESS == 0) && (DecRegs.MFBAHR18.bit.ADDRESS == 1))//if it's program flash 2;

{

zoiw_flash_key = PROGRAM_FLASH2_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR19.bit.ADDRESS == 0) && (DecRegs.MFBAHR19.bit.ADDRESS == 1))//if it's program flash 3;

{

zoiw_flash_key = PROGRAM_FLASH3_INTERLOCK_KEY;

}

else

{

return;

}

}

else if(arg1 == 3)//2 means end of fourth block;

{

zoiw_address = 0x1fff8;

if((DecRegs.MFBALR1.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR1.bit.ADDRESS == 1)) //here if flash block 0 is at 0x18000

//note that the address bits start at bit 10, so 0x20 in the address field equals 0x8000

{

zoiw_flash_key = PROGRAM_FLASH0_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR17.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR17.bit.ADDRESS == 1))//if it's program flash 1;

{

zoiw_flash_key = PROGRAM_FLASH1_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR18.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR18.bit.ADDRESS == 1))//if it's program flash 2;

{

zoiw_flash_key = PROGRAM_FLASH2_INTERLOCK_KEY;

}

else if((DecRegs.MFBALR19.bit.ADDRESS == 0x20) && (DecRegs.MFBAHR19.bit.ADDRESS == 1))//if it's program flash 3;

{

zoiw_flash_key = PROGRAM_FLASH3_INTERLOCK_KEY;

}

else

{

return;

}

}

else

{

return; //reject other arg1 values

}

for(counter=0; counter < 32; counter++) //Copy program from PFLASH to RAM

{

*(program_index++)=*(source_index++);

}

DecRegs.MFBALR1.bit.RONLY = 0; //enable program flash 1 write

DecRegs.MFBALR17.bit.RONLY = 0; //enable program flash 2 write

{

register FUNC_PTR func_ptr;

func_ptr=(FUNC_PTR)program_area; //Set function to program area

func_ptr();

} //execute erase checksum

DecRegs.MFBALR1.bit.RONLY = 1; //restore it to read only

DecRegs.MFBALR17.bit.RONLY = 1; //restore it to read only

SysRegs.SYSECR.bit.RESET = 2; //now reset processor.

break;

}

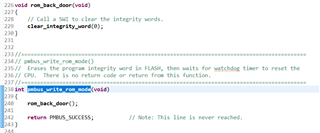

zero_out_integrity_double_word.c:

//###########################################################################

//

// FILE: zero_out_integrity_double_word.c

//

// TITLE:

//

// NOTES:

// 1)

//###########################################################################

//

// Ver | dd mmm yyyy | Who | Description of changes

// ======|=============|============|========================================

// 00 05 04 2015 HPCS

//

// Texas Instruments, Inc

// Copyright Texas Instruments 2008. All rights reserved.

//###########################################################################

#include "system_defines.h"

#include "cyclone_device.h"

#include "pmbus_commands.h"

#include "pmbus.h"

#include "variables.h"

#include "function_definitions.h"

#include "software_interrupts.h"

#pragma CODE_STATE(zero_out_integrity_double_word, 32) // this will ensure that this code builds in ARM mode

void zero_out_integrity_double_word(void) //clears integrity double word at address. using flash key provided

{

int i;

for(i = 0; i < 2; i++)

{

DecRegs.FLASHILOCK.all = zoiw_flash_key;

*(Uint32 *)(zoiw_address) = 0;

zoiw_address = zoiw_address + 4;

while((DecRegs.PFLASHCTRL_0.bit.BUSY != 0) || (DecRegs.PFLASHCTRL_1.bit.BUSY != 0) ||

(DecRegs.PFLASHCTRL_2.bit.BUSY != 0) || (DecRegs.PFLASHCTRL_3.bit.BUSY != 0))

{

; //do nothing while it programs

}

}

}

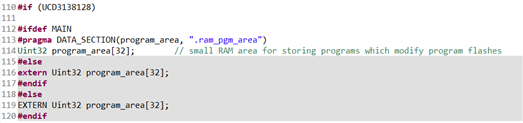

variables.h , program_area:

cyclone_128.cmd:

/*==========================================================================================

// cyclone.cmd Linker command file for Cyclone 128

//

//

// Available Cyclone 128 memory:

// ---------------------------------

// P-Flash 128K 0x00000 - 0x1fFFF

// ROM 8K 0x20000 - 0x21FFF

// D-Flash 2K 0x69800 - 0x69FFF

// RAM 8K 0x6A000 - 0x6BFFF

//

// Copyright (C) 2013 Texas Instruments Incorporated.

//========================================================================================*/

MEMORY

{

/*------------------------------------------------------------------------------------*/

/* ROM 8K 0x20000 - 0x21FFF */

/*------------------------------------------------------------------------------------*/

ROMVECS : org = 0x00020000, len = 0x00000020 /* Vector table */

ROM : org = 0x00020020, len = 0x00001D5E /* System ROM */

SINE : org = 0x00021D7E, len = 0x00000282 /* Sine table */

/*------------------------------------------------------------------------------------*/

/* P-Flash 128K 0x0 - 0x1FFFF //this one is set up for only 32K */

/*------------------------------------------------------------------------------------*/

FLASHVECS (RX) : org = 0x00000000, len = 0x00000020 /* PFlash "Re-vector" Table */

PFLASH (RX) : org = 0x00000020, len = 0x00007F34 /* PFlash Main Program */

DEVICEID (RX) : org = 0x00007F54, len = 0x00000020 /* Fixed Location for DEVICE_ID*/

FIXTFA (RX) : org = 0x00007F74, len = 0x00000004 /* Fixed Step Size for TFA */

FIXCONST (RX) : org = 0x00007F78, len = 0x00000080 /* Fixed-location Constants */

FLASHSUM (RX) : org = 0x00007FF8, len = 0x00000008 /* Flash Checksum */

/*------------------------------------------------------------------------------------*/

/* D-Flash 2K 0x69800 - 0x69FFF */

/*------------------------------------------------------------------------------------*/

DFLASH (RX) : org = 0x00069800, len = 0x00000800

/*------------------------------------------------------------------------------------*/

/* RAM 8K 0x6A000 - 0x6BFFF */

/* */

/* Partition RAM into 2 parts: */

/* 1. General variables. */

/* 2. Stacks for the various operating modes. */

/* NOTE!! Stack size must be specified in load.asm too!!! */

/*------------------------------------------------------------------------------------*/

RAM (RW) : org = 0x0006A000, len = 0x00001DD0

RAM_PGM_AREA (RW) : org = 0x0006BDD0, len = 0x00000080

STACKS (RW) : org = 0x0006BE50, len = 0x000001B0

}

SECTIONS

{

/*------------------------------------------------------------------------------------*/

/* P-Flash 32K 0x0 - 0x7FFF */

/* */

/* Most of these sections are unused for the ROM build. */

/*------------------------------------------------------------------------------------*/

.vectors : {} > FLASHVECS /* Interrupt "re-vectors" */

.fiq : {} > 0x001C /* Fast Interrupt Handler */

.text : {} > (PFLASH align(16)) /* Code */

.const : {} > (PFLASH align(16)) /* Constant data */

.cinit : {} > (PFLASH align(16)) /* Initialization tables */

FixedDeviceID : {} > (DEVICEID) /* Fixed location for Device ID */

FixedTfaStep : {} > FIXTFA /* Fixed location TFA Step Size */

FixedConstants : {} > FIXCONST /* Fixed location constants */

.flashi : {} > FLASHSUM /* PFlash Integrity Word */

/*------------------------------------------------------------------------------------*/

/* ROM (8kB 0x20000 - 0x21FFF */

/*------------------------------------------------------------------------------------*/

.romvectors : {} > ROMVECS

.sine : {} > SINE

/*------------------------------------------------------------------------------------*/

/* D-Flash 2K 0x69800 - 0x69FFF */

/*------------------------------------------------------------------------------------*/

.dflash : {} > (DFLASH align(32))

.CONFIG : {} > (DFLASH align(32))

.CONFIG_A : {} > (DFLASH align(32))

.CONFIG_B : {} > (DFLASH align(32))

.PASSW : {} > (DFLASH align(32))

/*------------------------------------------------------------------------------------*/

/* RAM 8K 0x6A000 - 0x6BFFF

/* Note, stacks must be defined in load.asm as well. */

/*------------------------------------------------------------------------------------*/

UNION : run = RAM_PGM_AREA

{

.ram_pgm_area

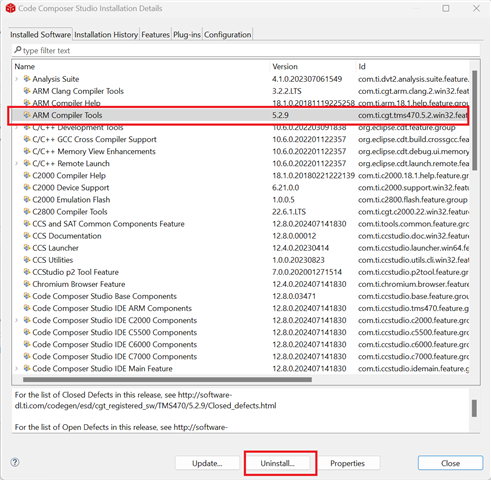

// .zero_out_integrity_word : load = PFLASH, start(_zero_out_integrity_double_word_start) {zero_out_integrity_double_word.obj }

.switch_active_program_to_pflash01 : load = PFLASH, start(_switch_active_program_to_pflash01_start) {switch_active_program_to_pflash01.obj }

.switch_active_program_to_pflash23 : load = PFLASH, start(_switch_active_program_to_pflash23_start) {switch_active_program_to_pflash23.obj }

}

.bss : {} > RAM /* Global & Static vars */

.stack : { /* total = 400 = 0x190 */

_StackUSER_ = . + 184; /* USER */

_StackFIQ_ = _StackUSER_ + 112; /* FIQ */

_StackIRQ_ = _StackFIQ_ + 84; /* IRQ */

_StackABORT_ = _StackIRQ_ + 4; /* ABORT */

_StackUND_ = _StackABORT_ + 4; /* UND */

_StackSUPER_ = _StackUND_ + 12; /* SUPER */

} > STACKS /* Software System stack */

}