Tool/software:

We have used the TPS65279 successfully for several years (using thousands of TPS65279). But recently we made a minor change in the layout and now we have problems with 70 % of the boards. I have not found the exact problem yet but while investigating I found a strange behaviour with one of the TPS65279 that are used on the board.

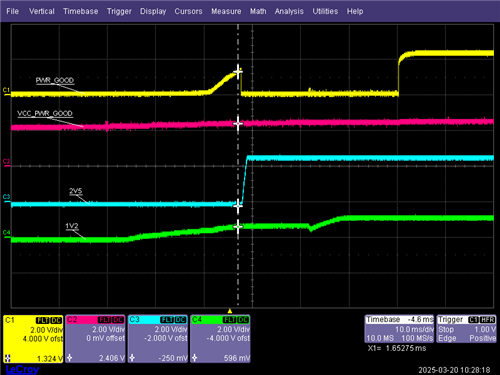

The PGOOD signals (or at least one of them, they are soldered together) from the TPS65279 sometime rises before the output voltages are valid:

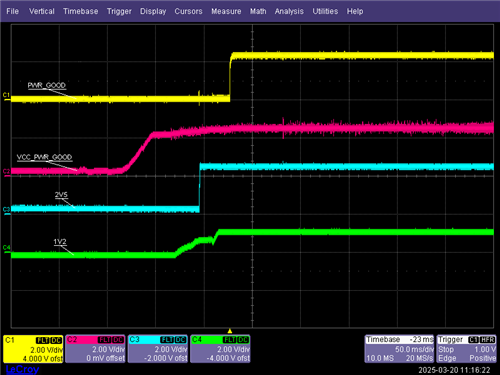

The normal behaviour looks like this (note that the horisontal scale is slightly changed):

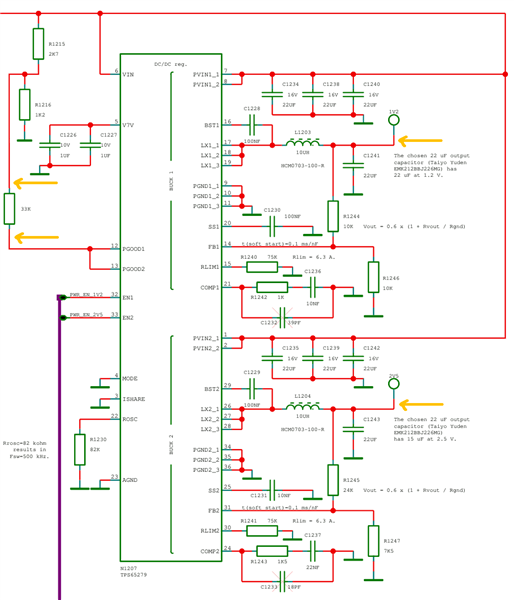

The schematic looks like:

VIN is 12 V. The yellow arrows indicate where the oscilloscope probes are placed.

The "glitch" on PGOOD is temperature sensitive. It almost always occur when the board has been powered off for a few minutes. But after running the board for perhaps 10 seconds it almost never occur. The current drawn from the 1V2 and 2V5 rails is very low when the board is being powered on, probably below 1 A.