Other Parts Discussed in Thread: UC3825, UC1825, TINA-TI

Tool/software:

Hello everyone,

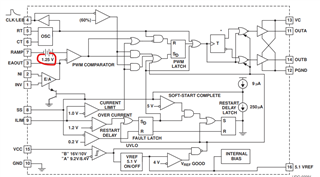

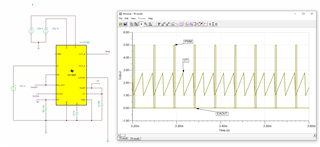

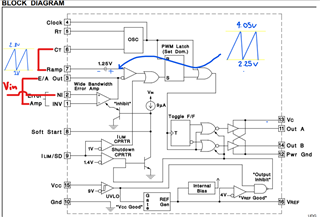

I have an issue with the UC3825 spice model (well the UC1825 that is provided on the UC3825 page), the issue is that on my simulation when I expect the PWM to be off I see some output, this is when EAout is 0V... when looking at the block diagram, I see that between the RAMP pin and the comparator is a voltage source with the negative side on the RAMP pin... if i look into the spice model, the negative side of the source seems connected to the comparator... V4 RAMP 22 1.25.... looking to other sources below, the arrangement looks ok.... V2 26 GND 1

Please advise.

Best Regards.