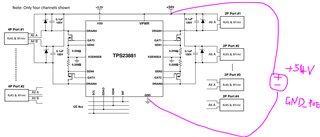

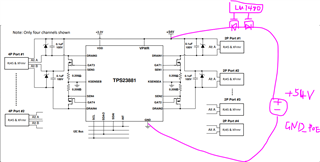

Other Parts Discussed in Thread: TS3A5018, TPS23881, , CSD18536KCS, LM7480

Tool/software:

Hi Sirs,

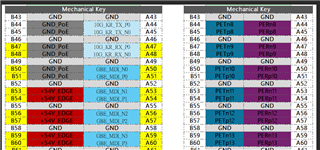

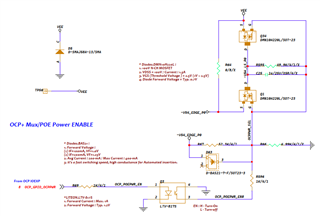

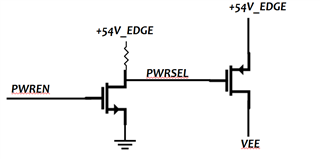

Current, I have an one power enable control design to asking as list, after will choice TI PMOS & NMOS combine solution ; but, not sure this idea is good or not?!

The project source will offer "-54V(negative)" power rail and possible setup off status for switch status(mean cut-off), then have external signal to control enable turn-on/off,

Here is the my design example :

[Noted : +54V_EDGE is equal to -54V(negative) power rail]

BRs

By Neil Chen