Other Parts Discussed in Thread: TPS65219

Tool/software:

Hello,

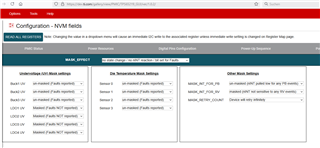

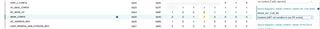

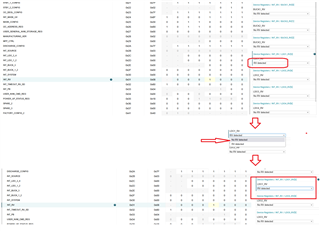

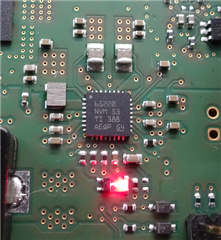

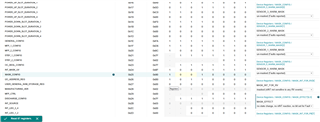

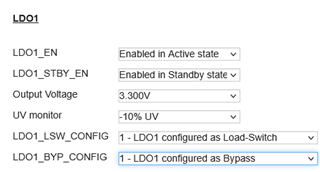

we've got a problem with the IC. In some cases the nINT pin toggles to low due to an RV event (most likely due to an external EMI event, not at start up). The voltage of all rails is still fine even if this happens and there seems no problem with the connected circuit which is powert by the PMIC; only the RV register of the one or other LOD indicates a problem. Therefore we tried to 'mask' this issue because our connected error LED is fired using the corresponding pin. However the nINT pin will still driven low. Also a cold reset using pin 28 works fine but the nINT is still low after that.

Is there a reason for 'mask' this isn't work as expected?

Is there bany other way to clear the corresponding register other to set is using I²C interface? If no, which command we have to send via I²C to clear the nINT register and toggle the pin back to high state?

What else we can do to prevent such issue?

tnx, Christian